Compile the design and program a device – Altera POS-PHY Level 4 IP Core User Manual

Page 19

Chapter 2: Getting Started

2–9

Compile the Design and Program a Device

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

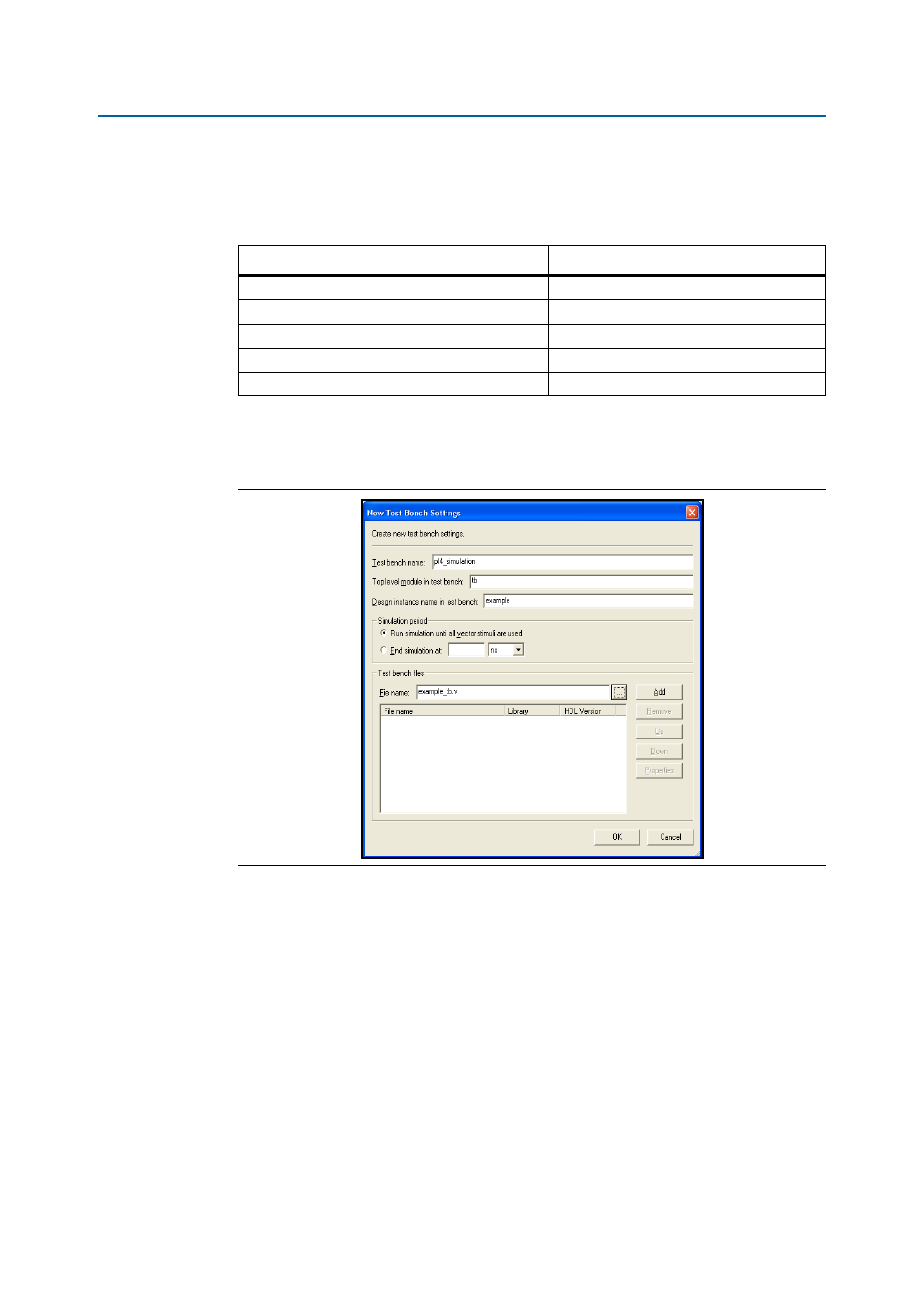

9. In the New Test Bench Settings dialog box, enter the information described in

Table 2–2 on page 2–9

(refer also to

Figure 2–6 on page 2–9

). To enter the files

described in the table, browse to the files in your project.

Figure 2–6 on page 2–9

shows an example of the testbench settings whxen the

10. When you have entered the required information for your new testbench, click OK

in the New Test Bench Settings dialog box.

11. Click OK in the Test Benches dialog box and then click OK in the Settings dialog

box.

12. Click Tools > EDA Simulation Tool, and then click Run EDA RTL Simulation

Tool

. The simulation now begins with your chosen simulation tool.

Compile the Design and Program a Device

You can use the Quartus II software to compile your design. Refer to Quartus II Help

for instructions on compiling your design.

Table 2–2. NativeLink Test Bench Settings

Parameter

Setting and File Name

Test bench name

<any name>

Top-level module in test bench

tb

Design instance name in test bench

<variation name>

Run for

100 ns

Test bench files

<variation name>_tb.v

Figure 2–6. Example of New Test Bench Settings for NativeLink