Atlantic interface error detection and handling – Altera POS-PHY Level 4 IP Core User Manual

Page 56

4–18

Chapter 4: Functional Description—Receiver

Error Flagging and Handling

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

The DIP-4 out-of-service status signal does not affect the data portion of the receiver.

However, it does affect the status channel portion, causing framing to be sent to the

adjacent device.

When reset, the stat_rd_dip4_oos flag is asserted (high). It remains asserted until the

reset is deasserted and a good_level number of consecutive control words that do not

contain DIP-4 errors are received.

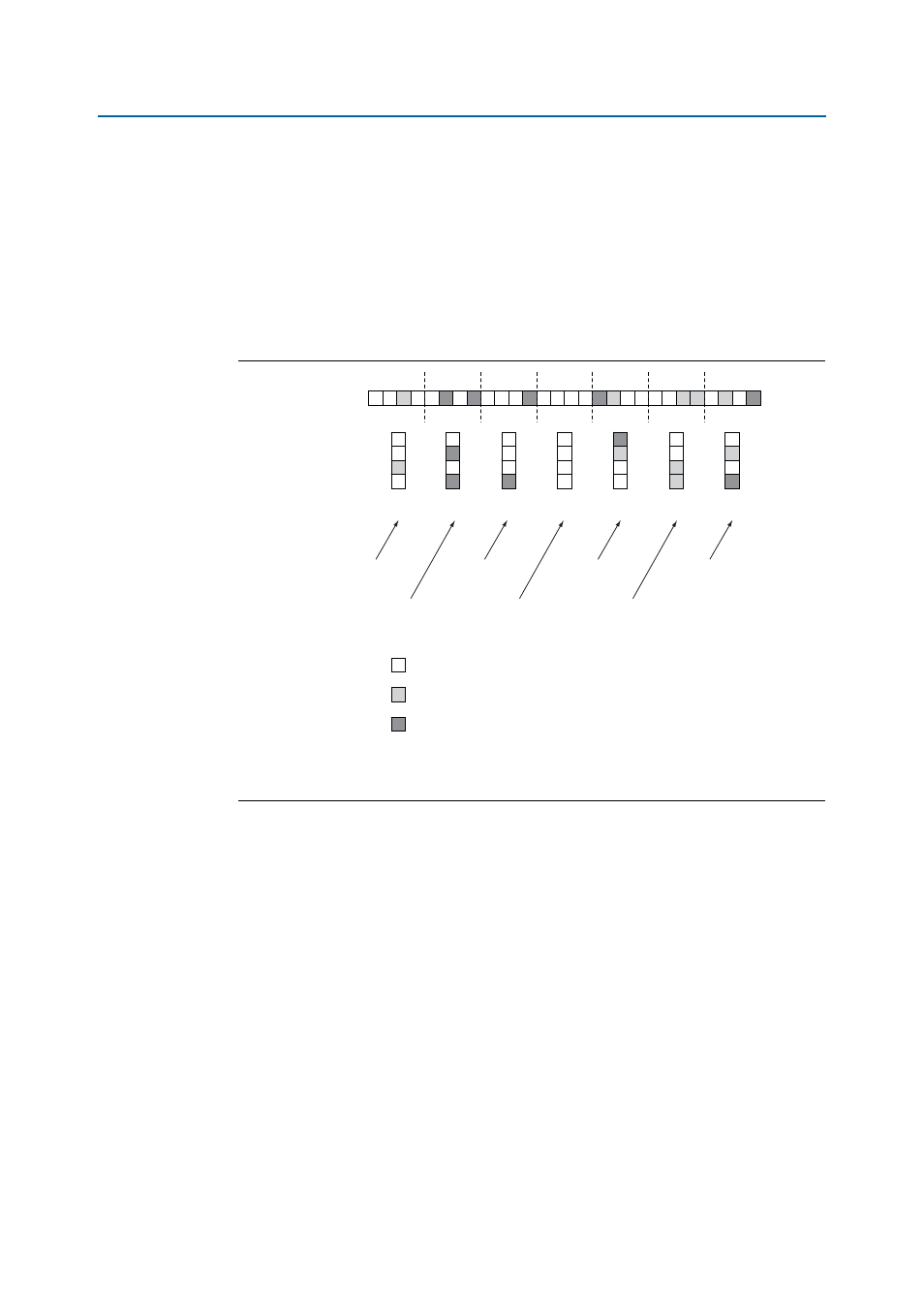

shows an example of the DIP-4 counter, where the receiver is in service

state and bad threshold is 3.

f

For further information on the DIP-4, refer to the System Packet Interface Level 4 (SPI-4)

Phase 2 Revision 1: OC-192 System Interface for Physical and Link Layer Devices, available

at

Atlantic Interface Error Detection and Handling

When the Atlantic error checking parameter is turned on, a filtering block—the

Atlantic FIFO buffer error checker—is instantiated at the write side of the FIFO buffer

to ensure that the IP core does not pass errored packets.

Figure 4–8. DIP-4 Counter

(Note 1)

Notes to

(1) Receiving a good and a bad DIP-4 in the same parallel cycle resets the counter (does not increment it), so that OOS

does not trigger.

0

1 2 2 0

0

0

Non-control word (payload)

Control word witih good DIP-4

Control word with bad DIP-4

SPI-4.2 Bus

Internal Parallel

Bus (Four-Lane)

Bad DIP-4 Counter

Resets

Counter

Increments by 1

Increments by 1

Unchanged

Resets

Counter (1)

Resets

Counter

Resets

Counter