Features – Altera POS-PHY Level 4 IP Core User Manual

Page 4

1–2

Chapter 1: About This IP Core

Features

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

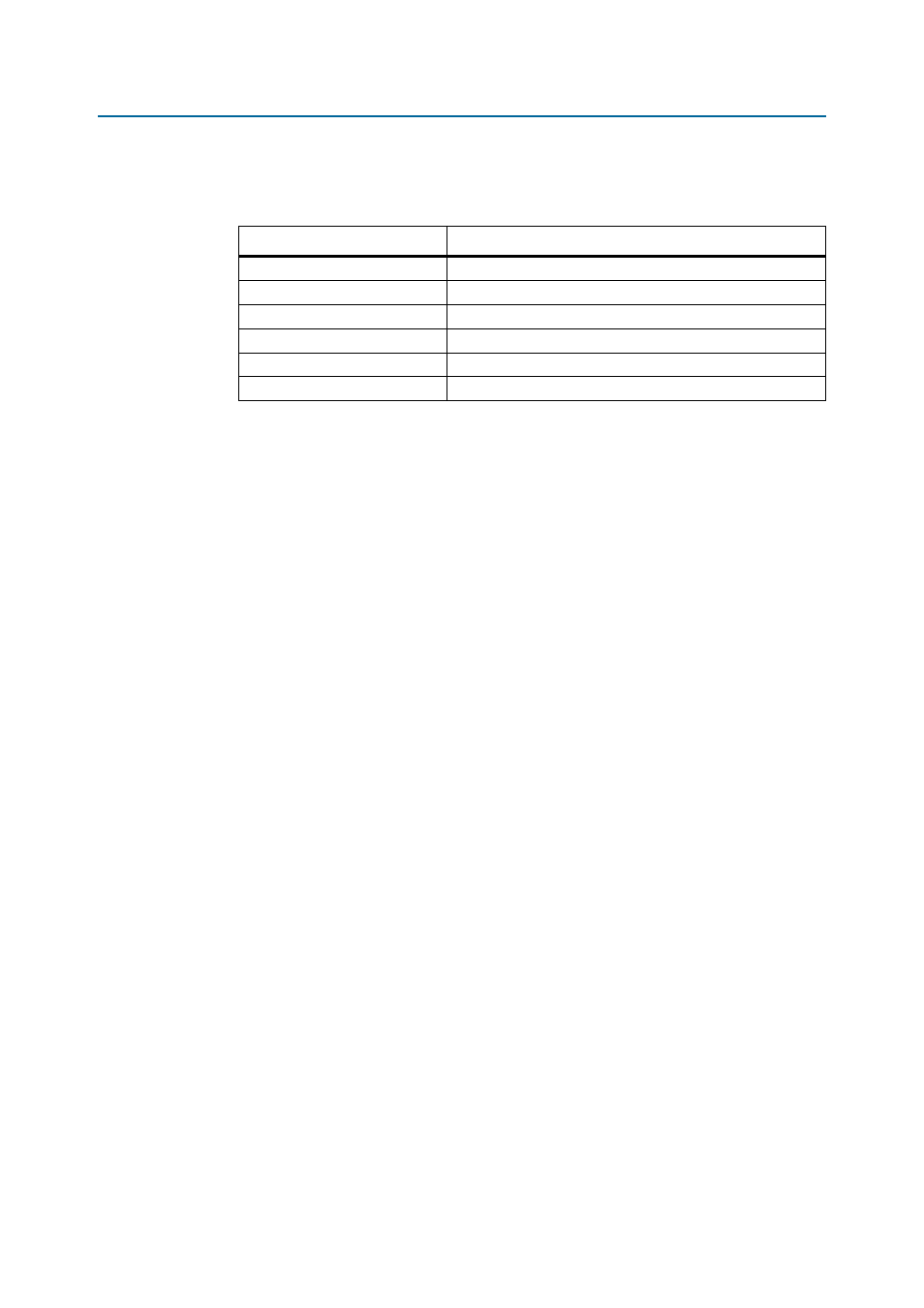

Table 1–3

shows the level of support offered by the POS-PHY Level 4 IP core to each

Altera device family.

Features

■

Compliant with all applicable standards, including:

■

Optical Internetworking Forum (OIF), System Packet Interface Level 4 (SPI-4)

Phase 2 Revision 1: OC-192 System Interface for Physical and Link Layer Devices,

OIF-SPI4-02.1, October 2003.

■

PMC-Sierra Inc., POS-PHY

TM

Level 4 A Saturn Packet and Cell Interface

Specification for OC-192 SONET/SDH and 10 GB/s Ethernet Applications, Issue 5

(Draft): June 2000.

■

Stratix III, Stratix IV, and Stratix V device support up to 1,250 Mbps and Stratix II

device support up to 1,040 Mbps, including integrated dynamic phase alignment

(DPA) hardware module

■

Cyclone III, device support up to 622 Mbps for 64 bit data path; support up to 250

Mbps for 32-bit data path width

■

Configurable data path width—affecting the IP core size and speed—for various

performance requirements and applications:

■

128 bits

■

64 bits

■

32 bits (quarter rate)

■

Supports up to 256 ports

■

Fixed start of packet (SOP) alignment to the most significant byte lane eases

subsequent packet processing

■

First-in first-out (FIFO) buffer status management and indications

■

Configurable FIFO buffer modes

■

Shared buffer with embedded addressing

■

Individual buffers

Table 1–3. Device Family Support

Device Family

Support

Arria

®

II GX

Preliminary

Arria II GZ

Preliminary

Cyclone IV

Preliminary

Stratix IV

Full

Stratix V

Preliminary

Other device families

No support