Receiver testbench examples – Altera POS-PHY Level 4 IP Core User Manual

Page 101

Chapter 6: Testbench

6–3

Receiver Testbench Examples

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

There are three pattern generation functions capable of generating idles, training

patterns, and data packets.

Table 6–2

shows the format of each function.

All of the packets are sent in sequence with no breaks between them. However, idles

can be inserted by adding the idle command in the testbench data generation section.

After all packets have been sent, the idle pattern is repeated until the end of the

simulation.

The testbench concludes by checking that all of the packets have been received. In

addition, it checks that the Atlantic packet receivers (data analyzer modules, one for

each port) have not detected any errors in the received packets. If no errors have been

detected, and all packets have been received, the testbench issues a message stating

that the simulation is successful.

If errors have been detected, a message states that the testbench has failed. If not all

packets have been detected, a message states that the testbench is incomplete. The

tb.exp_chk_cnt

variable determines the number of checks done to ensure

completeness of the testbench. For each port tested, one completeness check is done.

In addition, a final check is done for the conclusion of the testbench.

Optionally, the testbench can create backpressure on the SPI-4.2 interface. When the

backpressure variable is defined, backpressure is generated on one or more ports by

first turning off the data analyzer receiver for the appropriate port. As the receive

FIFO buffer begins to fill, it goes from the hungry state to the satisfied state. When the

FIFO buffer is satisfied, the status on the SPI-4.2 interface notifies the packet

generation module to stop sending data. There is a break in packet generation during

which idles are sent. After the status returns to the hungry state, the packet generation

resumes.

Receiver Testbench Examples

In addition to the tasks described in

Table 6–2 on page 6–3

, the packet generation

module also has the following four tasks, which you can use to generate error signals

when running the testbench:

■

pkt2

■

task_cw

■

task_cw2

■

task_pay

Table 6–3

describes the four error generation tasks in more detail.

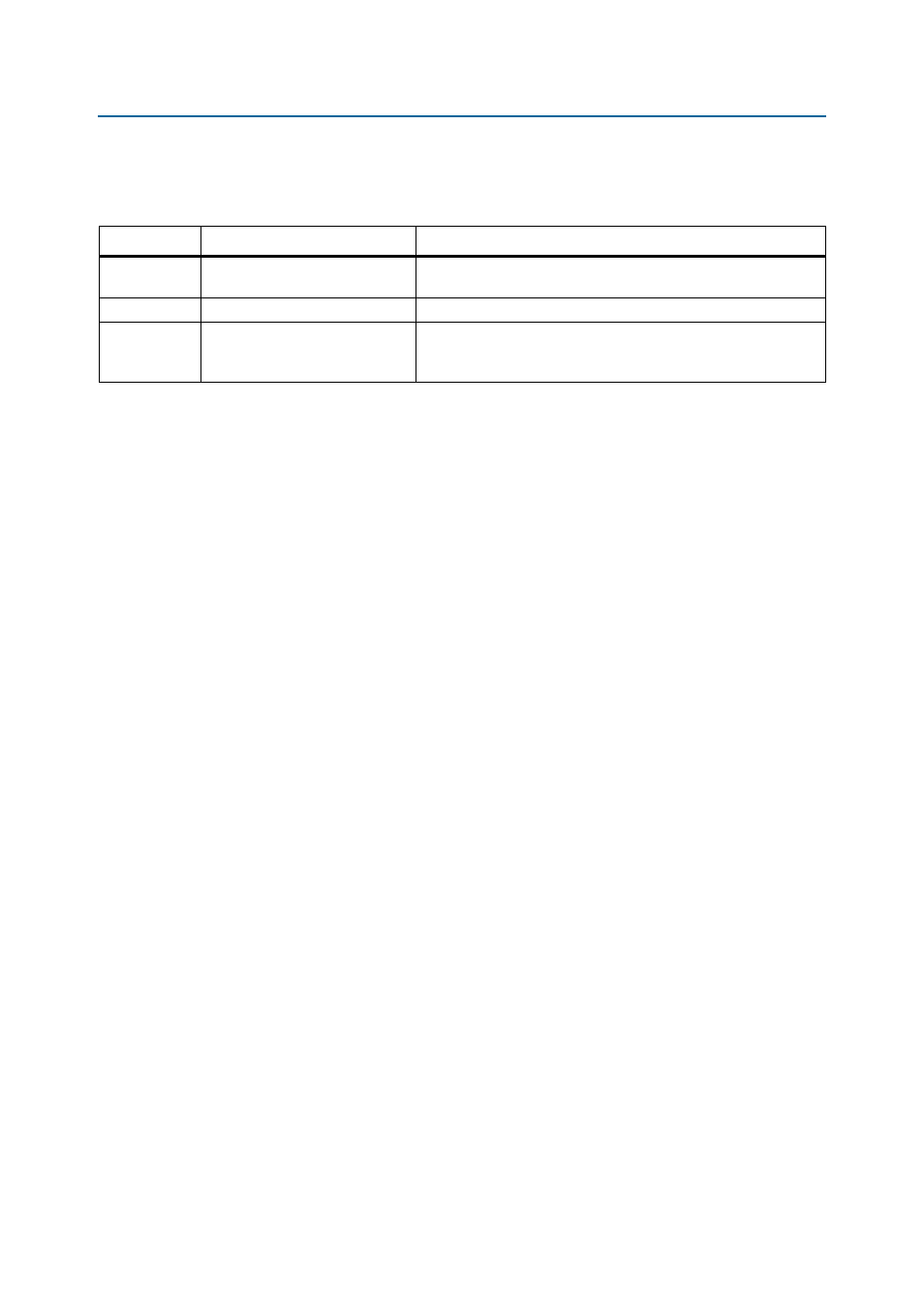

Table 6–2. Function Format

Command

Format

Description

Training

pattern

spi_gen.tp (width, number)

width

is the number of clock cycles the training pattern takes;

number

is the number of training pattern sequences.

Idle

spi_gen.idles (number) number

is the number of sequential idles

Data packet

spi_gen.pkt (port_number,

err, size, num)

port_number

is the target port for the packet. err is set to zero;

size

is the packet size in bytes (2-2

16

bytes); num is the packet

sequence number.