General description – Altera POS-PHY Level 4 IP Core User Manual

Page 5

Chapter 1: About This IP Core

1–3

General Description

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

■

Error detection and handling

■

Protocol checking—SPI-4.2 datapath state machine check and repair

■

Atlantic FIFO buffer overflow handling

■

Status framing hysteresis (good and bad thresholds)

■

DIP-4 hysteresis (good and bad thresholds)

■

IP functional simulation models for use in Altera-supported VHDL and Verilog

HDL simulators

■

I-Tested certification

General Description

The packet over SONET/SDH physical layer (POS-PHY) Level 4 interface, first

developed by the SATURN

®

Development Group, was adopted by the Optical

Internetworking Forum (OIF) as the System Packet Interface Level 4—Phase 2 (SPI-

4.2). Therefore, POS-PHY Level 4 and SPI-4.2 are synonymous.

The POS-PHY Level 4 IP core uses the SPI-4.2 interface for high-speed cell and packet

transfers between physical (PHY) and link-layer devices. The SPI-4.2 interface

supports a data width of 16 bits (LVDS solution) and can be a PHY-link, link-link, link-

PHY, or PHY-PHY connection in multi-gigabit applications, including: asynchronous

transfer mode (ATM) and packet over SONET/SDH (STS-192/STM-64), 10 Gigabit

Ethernet, and multi-channel Gigabit and Fast Ethernet.

In compliance with the SPI-4.2 interface specification, the POS-PHY Level 4 IP core

allows you to implement transmit and receive functions.

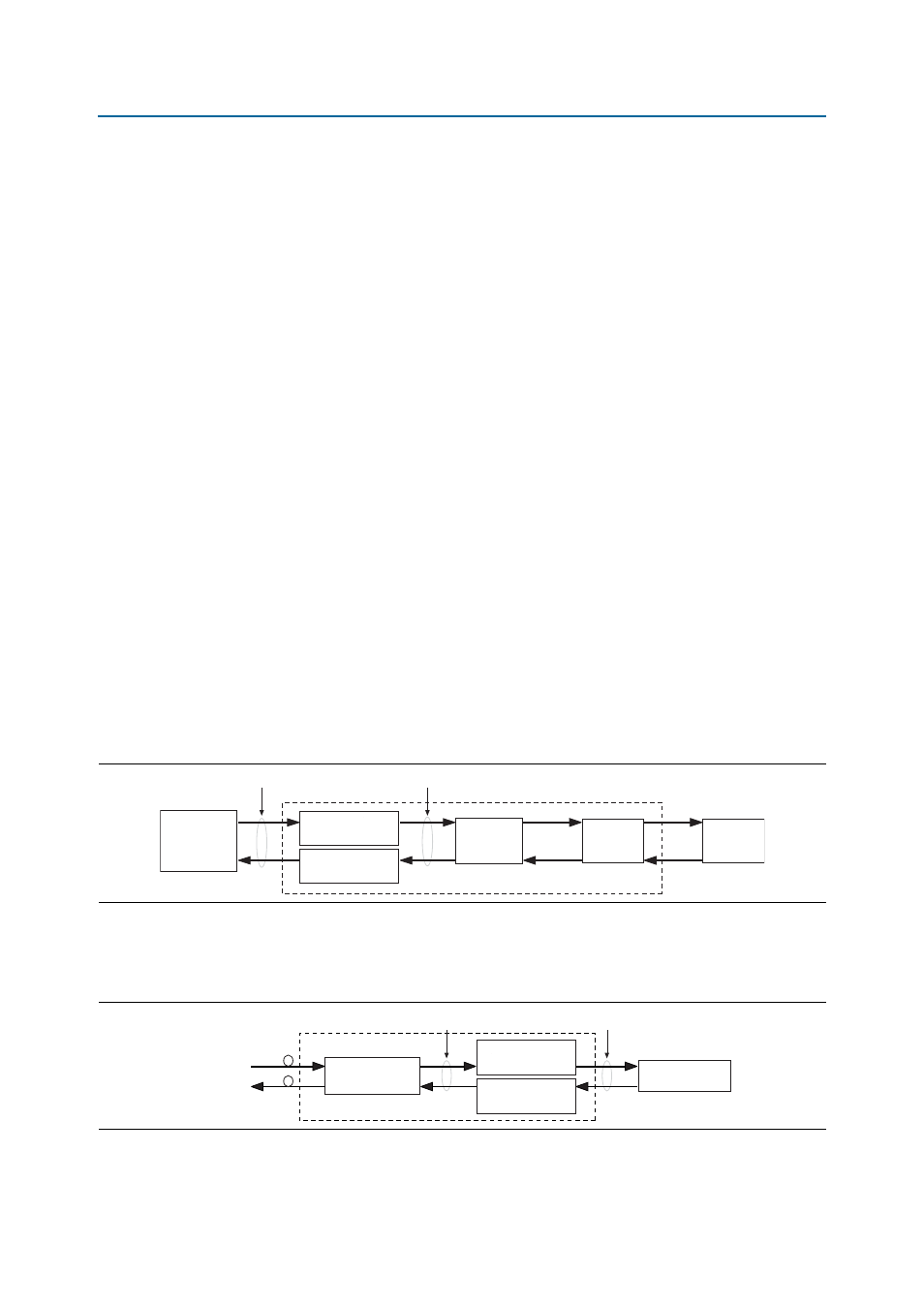

Figure 1–1

shows a full-duplex POS-PHY Level 4 IP core configured for the link layer

in an Altera FPGA device.

Figure 1–2

shows a full-duplex POS-PHY Level 4 IP core configured for the PHY layer

in an Altera FPGA device.

Figure 1–1. POS-PHY Level 4 IP Core as Link Layer Configuration

FPGA

SPI-4.2 Interface

Switch

Interface

User Packet

Processing

OC-192

POS Framer

or

10 GbitE MAC

Switch

Fabric

Atlantic Interface

POS-PHY Level 4

Receiver

POS-PHY Level 4

Transmitter

Figure 1–2. POS-PHY Level 4 IP Core as PHY Layer Configuration

OC-192 or

10 GbitE

FPGA

Framer or MAC

Logic

Packet

Classifier

SPI-4.2 Interface

Atlantic Interface

POS-PHY Level 4

Receiver

POS-PHY Level 4

Transmitter