Altera POS-PHY Level 4 IP Core User Manual

Page 103

Chapter 6: Testbench

6–5

Receiver Testbench Examples

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

Table 6–4

gives examples of how to simulate the 12 error conditions in the IP core by

running the packet generation tasks in the testbench module. When simulating errors

on the SPI-4.2 interface, you must turn off error checking on the testbench interface by

using the following tasks:

■

To disable the missing EOP check on the POS-PHY Level 4 interface:

spi_gen.check_meop = 1’b0;

■

To disable the missing SOP check on the POS-PHY Level 4 interface:

spi_gen.check_msop = 1’b0;

■

To disable error checking on the data analyzer interface:

sapmon.checking(1’b0);

spi_gen.cw2

(cw_type,eops[1:0],sop,

port[7:0],dip4err)

Similar to the cw task,

but has separate

arguments for each

control word field.

DIP4 is auto

calculated and

inserted, and it can be

inverted.

cw_type

sets the control word type, in accordance with

the POS-PHY4 specification.

eops[1:0]

sets the EOP status, in accordance with the

POS-PHY4 specification.

sop

sets the SOP status, in accordance with the POS-

PHY4 specification.

port[7:0]

sets the port address.

When the dip4_err bit is set, the DIP4 calculation is

inverted.

spi_gen.pay (data[15:0])

Sends a payload data

burst for one cycle.

dat[15:0]

sets the payload data bytes.

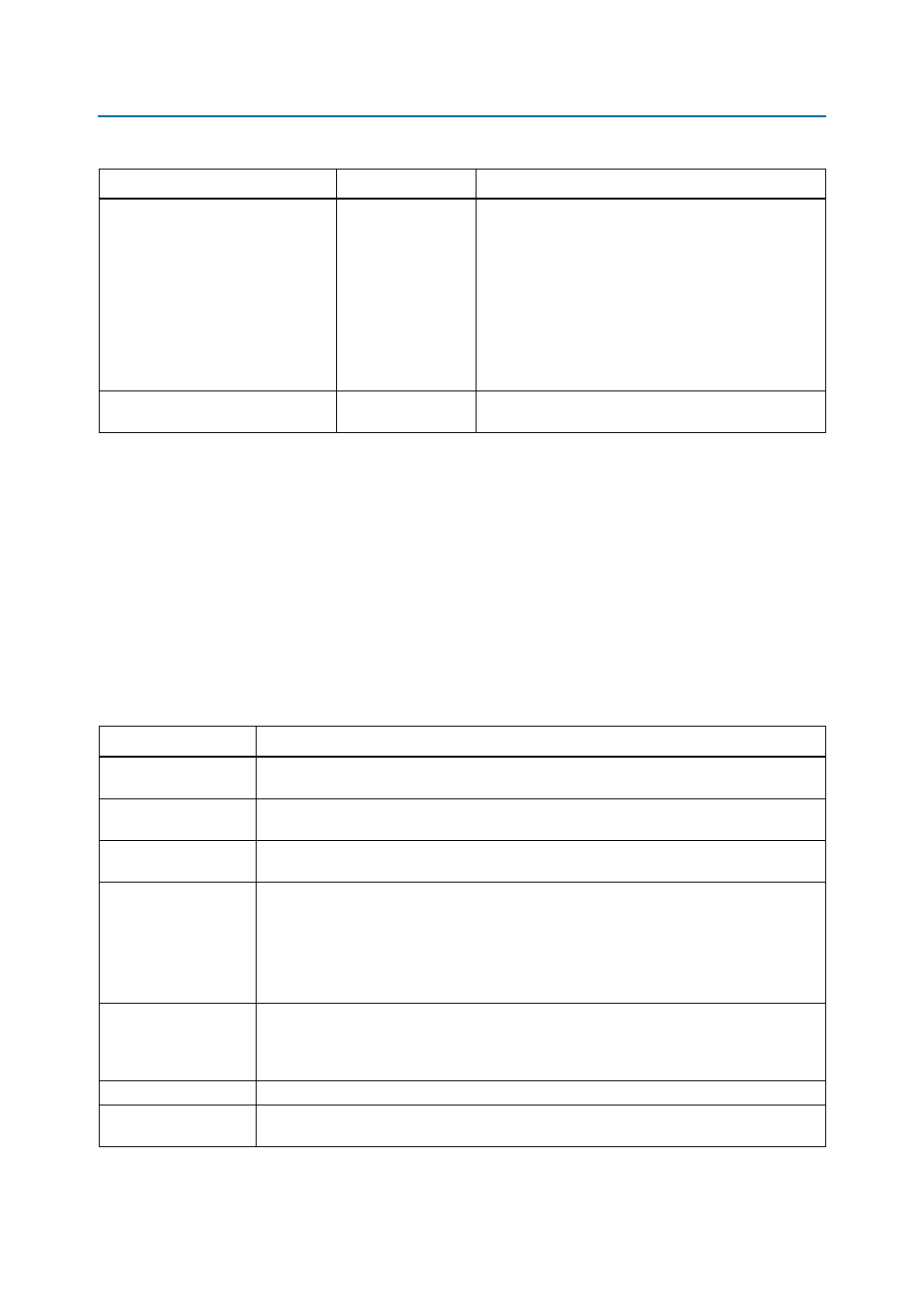

Table 6–3. Error Generation Tasks in the Packet Generation Module

Task Format

General Description

Input Parameters Description

Table 6–4. Error Simulation Using the Testbench Module (Part 1 of 2)

Error Signal

Testbench Simulation

err_ry_meop

Using the pkt2 task, send in packets with error code 3:

spi_gen.pkt2(

err_ry_msop

Using the pkt2 task, send in packets with error code 2:

spi_gen.pkt2(

err_ry_paddr

Using the pkt2 task, send in a packet with an address greater than the setting for number of

ports.

err_ry_fifo_oflw

Turn off the data analyzer interface:

sapmon.port0.stop;

spi_gen.idles(10);

Send in a large packet:

spi_gen.next_pkt2(

err_rd_dpa

This error signal can only be asserted on a Stratix GX device. Delay one of the bits of the Rx SPI-

4.2 bus by more than the tolerable amount of 4.5,:

delay.bit_delay(/*rctl*/0, /*rdat*/9, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0, 0,

0, 0, 0);

err_rd_abuf_oflw

This error signal cannot be simulated with this version of the testbench.

err_rd_eightn

Using the pkt2 task, send in a packet with a missing EOP and a non 16-byte multiple length:

spi_gen.pkt2(