Avalon-mm interface register map – Altera POS-PHY Level 4 IP Core User Manual

Page 94

5–24

Chapter 5: Functional Description—Transmitter

Avalon-MM Interface Register Map

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Avalon-MM Interface Register Map

Table 5–10

lists the Avalon-MM interface registers.

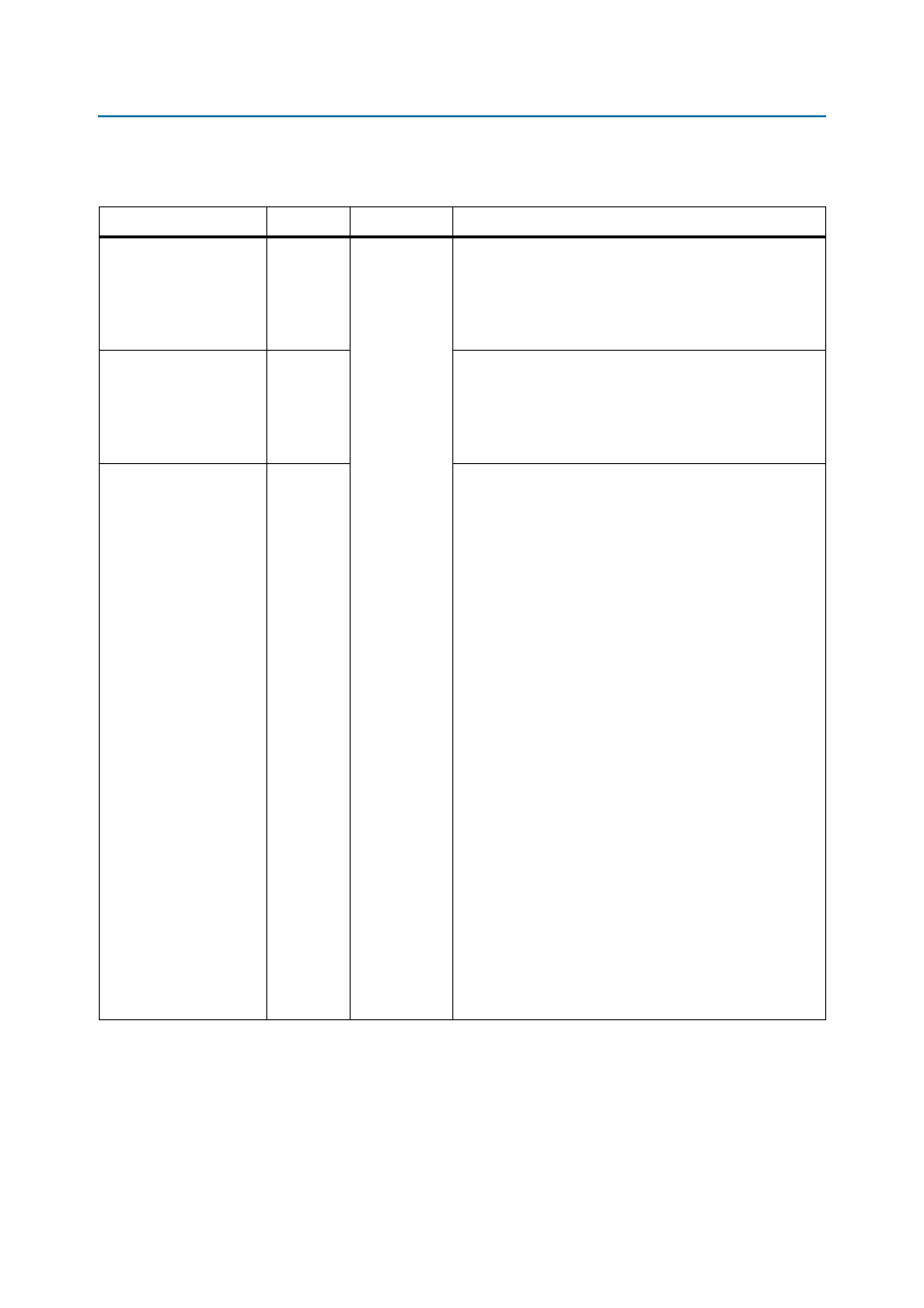

Table 5–9. Scheduler Control and Status

Signal

Direction

Clock Domain

Description

ctl_td_mb1[10:0]

Input

tdint_clk

Maximum number of bytes that can be transmitted when the

downstream FIFO buffer is starving. This number does not

imply that a control word is inserted. Units are in bytes.

Supports 0 to 2,032 bytes in 16-byte increments. This port is

absent if you turn on Shared Buffer with Embedded

Addressing.

ctl_td_mb2[10:0]

Input

Maximum number of bytes that can be transmitted when the

downstream FIFO buffer is hungry. This number does not

imply that a control word is inserted. Units are in bytes.

Supports 0 to 2,032 bytes in 16-byte increments. This port is

absent if you turn on Shared Buffer with Embedded

Addressing.

ctl_td_

switchmode[1:0]

Input -

Static reset

This input determines the port switching behavior of the

scheduler.

■

The scheduler always makes a port switch decision when

ctl_td_burstlen

data is sent, or when an EOP is sent.

■

Next credits are held in a table for all ports, and are

incremented by status updates.

■

Current credits are stored in a separate register for a single

port while it is serviced, and become stale because status

updates do not increment the value.

■

A port is only eligible for scheduling if there are greater

than or equal to ctl_td_burstlen next credits available,

and greater than or equal to ctl_td_burstlen data

available in the corresponding Atlantic FIFO buffer.

■

When ‘00’ (switch on EOP is turned off) the scheduler

switches when less than ctl_td_burstlen current

credits are available, or less than ctl_td_burstlen data

is available in the Atlantic buffer.

■

When ‘01’ (switch on EOP is turned on), the scheduler

switches when less than ctl_td_burstlen current

credits are available, or less than ctl_td_burstlen data

is available in the Atlantic buffer, or an EOP is sent.

■

When ‘10’ or ‘11’, the scheduler switches when

ctl_td_burstlen

data is sent, or an EOP is sent.

■

In the IP Toolbench top-level file, the upper bit is always

tied to zero, and the lower bit is tied depending on the value

of the switch on end of packet feature. This port is absent if

you turn on Shared Buffer with Embedded Addressing.

Only change at reset.