Clock structure, Single clock mode, Multiple clock mode – Altera POS-PHY Level 4 IP Core User Manual

Page 47

Chapter 4: Functional Description—Receiver

4–9

Clock Structure

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

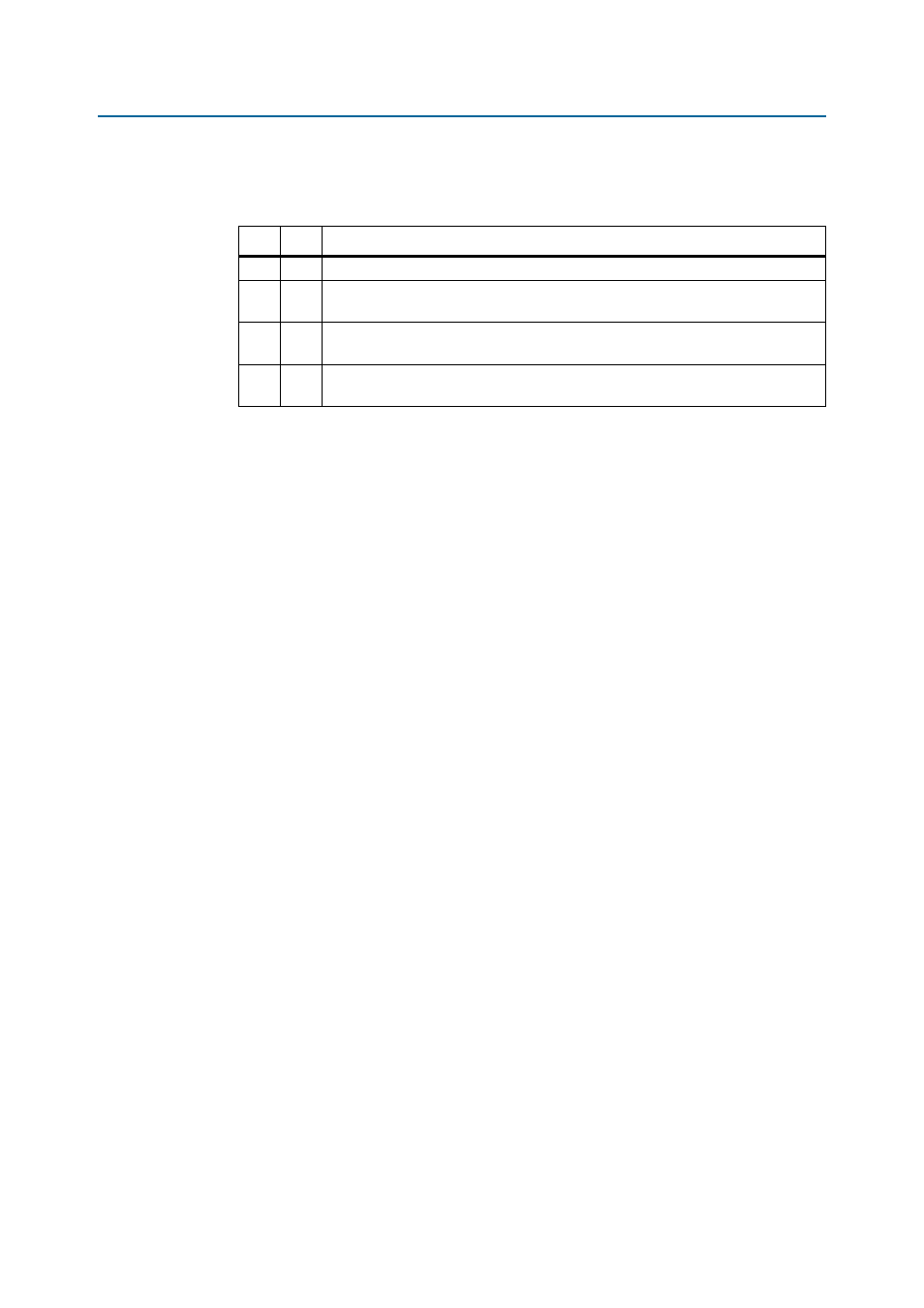

The FIFO buffer status of each port is encoded in 2 bits (refer to

Table 4–1

) and is

transmitted synchronous to the rsclk.

Clock Structure

With the Atlantic FIFO buffer clock mode parameter in IP Toolbench, you can

parameterize the receiver in one of the following two clocking structures:

■

Single clock mode

■

Multiple clock mode

The IP core uses a common clocking structure for all data path width variations.

1

All clocks are asynchronous and paths between the domains can be cut.

The receiver has two primary clock domains. The first clock domain is associated with

the SERDES and logic directly connected to the SPI-4.2 interface; the second clock

domain is associated with the Atlantic interface and the bulk of the receiver logic. The

clock for the first domain is derived from the rdclk of the SPI-4.2 interface. This clock,

rdint_clk

, is available as an output from the IP core, and is the output of the PLL for

the ALTLVDS block. For Stratix GX devices, an extra PLL generates the rdint_clk

clock.

f

For advanced information on the requirements of rxsys_clk, refer to

Optimum Frequency for rxsys_clk

Single Clock Mode

In the single clock mode, the Atlantic FIFO buffers are instantiated as single clock

domain buffers, thereby consuming fewer logic resources.

Multiple Clock Mode

If you select the multiple clock domain mode, the rxsys_clk clock clocks the protocol

logic of the IP core, and the write side of the Atlantic FIFO buffers.

Table 4–1. Status Channel Field Descriptions

MSB

LSB

Description

1

1

Reserved for framing

1

0

SATISFIED—FIFO buffer is almost full. No new credits should be granted in the far

end scheduler.

0

1

HUNGRY—FIFO buffer is at a midpoint. MaxBurst2 credits should be granted in the

far end scheduler.

0

0

STARVING—FIFO buffer is almost empty. MaxBurst1 credits should be granted in

the far end scheduler.

Note to

Table 4–1

:

(1) Worst case, up to MaxBurst1 16-byte units—plus the amount of data in transit due to data and status latency—

may still be received, regardless of the current status transmitted.