Altera POS-PHY Level 4 IP Core User Manual

Page 108

A–2

Appendix A: Start-Up Sequence

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

1

For a 32-bit transmitter IP core, no PLLs are used so the ctl_tx_pll_areset and

stat_rx_pll_locked

signals do not exist.

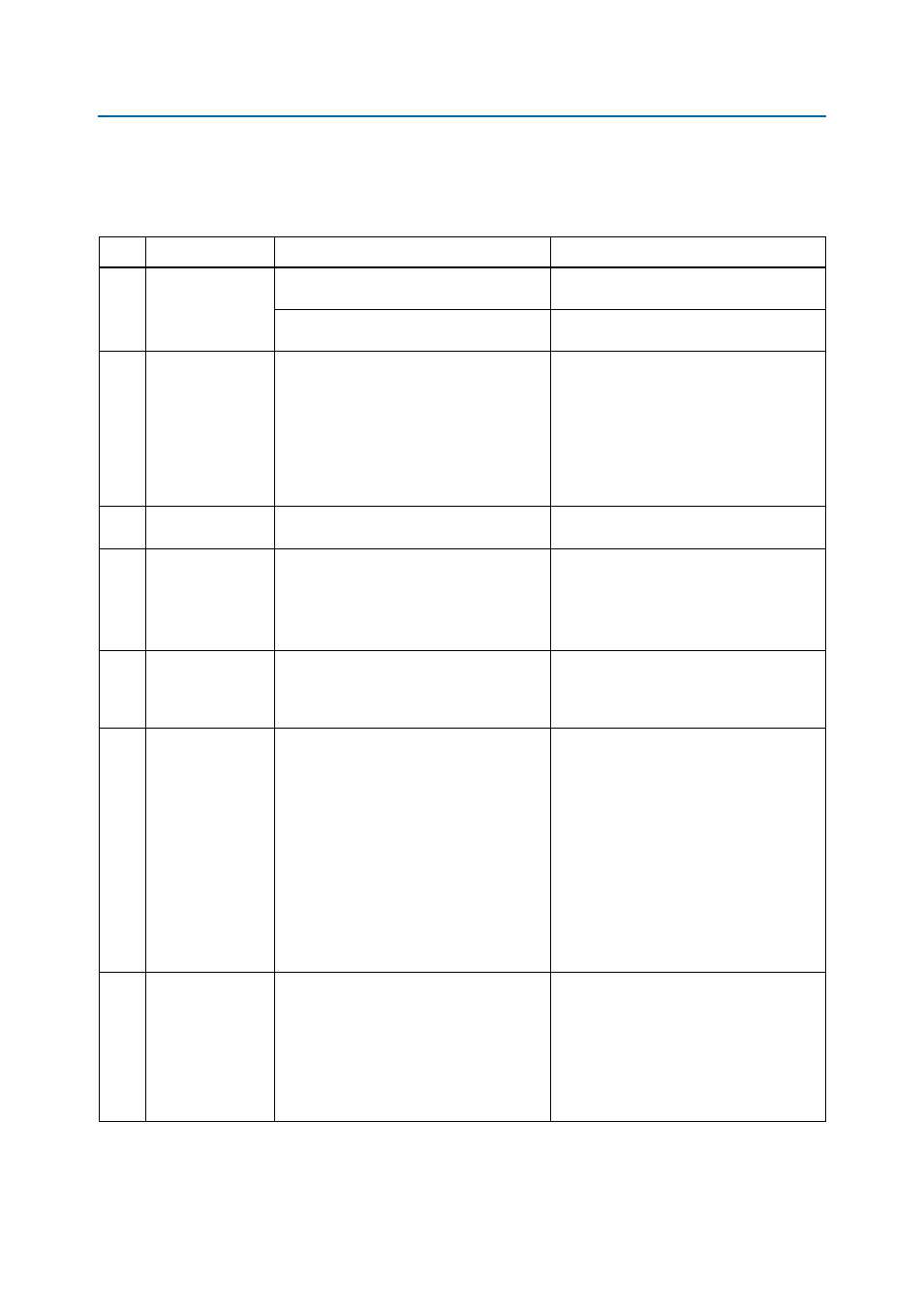

Table A–1. Start-Up Sequence (Part 1 of 2)

Event

Description

Receiver IP Core

Transmitter IP Core

1

Power Up

Assert ctl_rx_pll_areset and

rxreset_n

.

Assert ctl_tx_pll_areset and

txreset_n

.

The receiver IP core sends framing

pattern('b11) on rstat[1:0].

—

2a

Release PLL

areset

Release receiver PLL reset

(ctl_rx_pll_areset) after rdclk

stabilizes (timed). Wait for the receiver PLL to

lock (stat_rx_pll_locked).

After trefclk stabilizes, deassert the

transmitter PLL reset

(ctl_tx_pll_areset).

Wait for the transmitter PLL to lock

(stat_tx_pll_locked). Depending on the

source of trefclk, you can deassert the PLL

reset by observing a PLL locked signal,

waiting for a fixed amount of time, or both.

2b

Wait for other clock

to stabilize.

Wait for all the other clocks (aN_arxclk,

rxsys_clk

and rav_clk) to be stable.

Wait for all the clocks (aN_atxclk,

txsys_clk

and tav_clk) to be stable.

3

Release IP core

reset

Wait for at least 4 clock cycles of the

receiver’s slowest clock, then release the

receiver reset (rxreset_n).

Wait for at least 4 clock cycles of the

transmitter’s slowest clock, then release the

transmitter reset (txreset_n).

As soon as reset is released, the IP core

sends a continuous training pattern.

3

IP core

Configuration

(Optional)

If IP core configuration needs to be

performed, assert ctl_ry_rsfrm to disable

the status finite state machine (FSM) from

transmitting valid status information.

If IP core configuration needs to be

performed, assert ctl_ts_rsfrm to prevent

the IP core from attempting to frame, and

force it to send a continuous training pattern.

4

—

If Asymmetric Port Support and/or Hitless

B/W Reprovisioning is turned on, set up the

calendar parameters using the Avalon

®

Memory-Mapped (Avalon-MM) interface

(refer to

Appendix E, Programming the SPI-

4.2 Calendar via the Avalon Memory-Mapped

Interface

for details). Once the IP core

configuration is complete deassert

ctl_ry_rsfrm

. All the IP core parameters

(signals that start with ctl_) must be stable

before releasing ctl_ry_rsfrm.

The IP core may transmit a valid status frame

if the training is complete.

If Asymmetric Port Support and/or Hitless

B/W Reprovisioning is turned on, set up the

calendar parameters using the Avalon-MM

interface (refer to

the SPI-4.2 Calendar via the Avalon Memory-

Mapped Interface

for details). Once the IP

core configuration is complete deassert

ctl_ts_rsfrm

. All the IP core parameters

(signal that start with ctl_) must be stable

before releasing ctl_ts_rsfrm.

The status framer searches for a valid status

frame.

5a

Trained—DPA

variations of

receiver IP cores

DPA circuitry locks onto the training pattern

(1 to approximately 1,000 training repetitions

are required). Stratix IV, Stratix III, Stratix II,

and Stratix GX devices indicate altlvds DPA

has locked by asserting

stat_rd_dpa_lvds_locked

. DPA channel

aligner lock is indicated by

stat_rd_dpa_locked

.

—