Altera POS-PHY Level 4 IP Core User Manual

Page 93

Chapter 5: Functional Description—Transmitter

5–23

Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

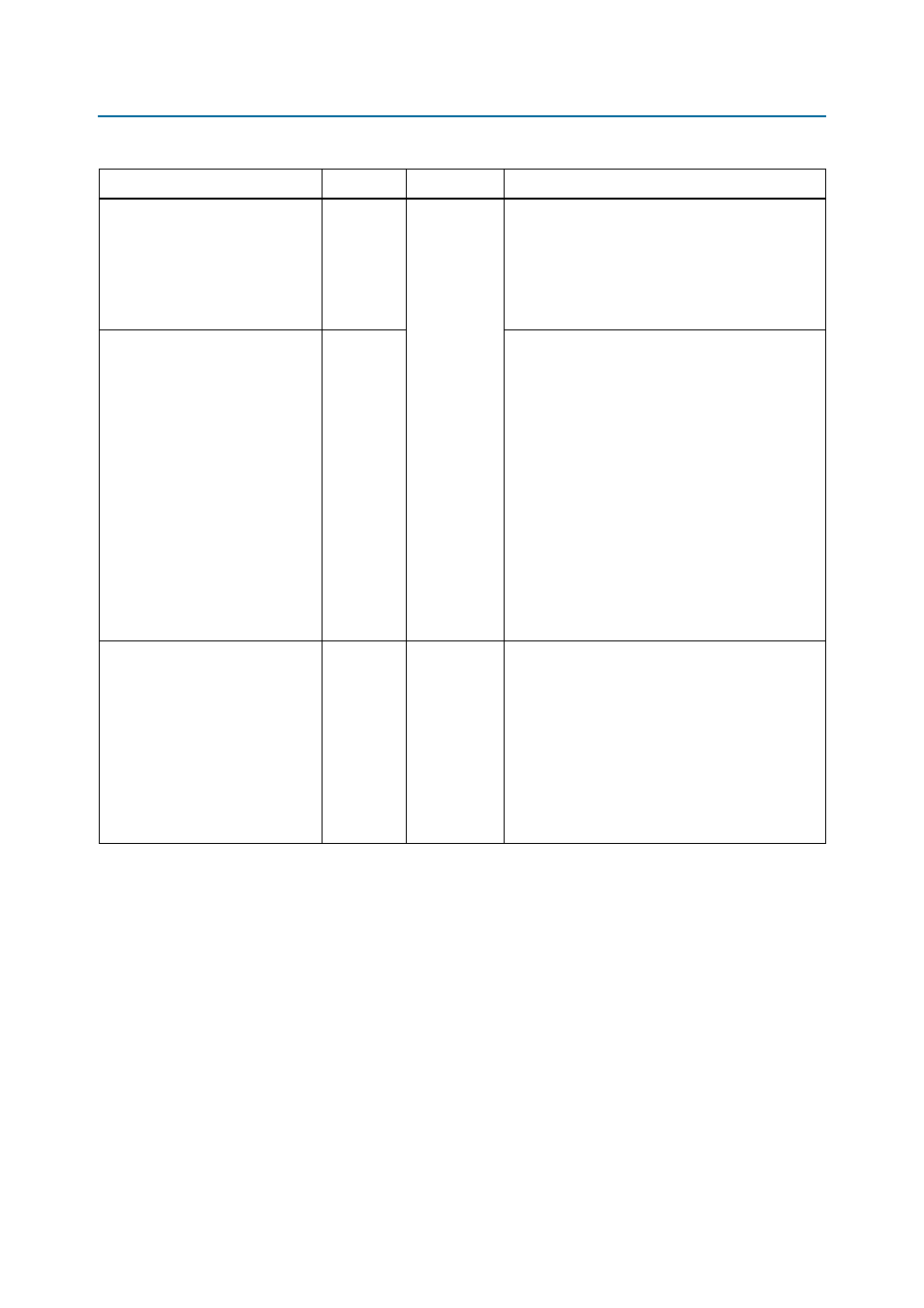

ctl_td_alpha[7:0]

Input

tdint_clk

Number of training pattern sequence repetitions. This

value only applies to interval training patterns. If a

training pattern is inserted due to stat_ts_sync

deasserted, the training pattern lasts until

stat_ts_sync

is asserted, and the current 20-cycle

training pattern completes. Setting to zero results in

an ALPHA of 256. Only change at reset.

ctl_td_burstlen[9:0]

Input

■

For the individual buffers mode, this input sets the

legal burst unit size, formerly known as burst

length. A burst must end on either a non-zero

multiple of ctl_td_burstlen, or on an EOP.

■

For the shared buffer with embedded addressing

mode, this input only limits when the IP core may

read data from the buffer. This input enables

delineating bursts, as in the individual buffers

case, only if the user logic pushes bursts into the

buffer with the desired delineation.

■

In either mode, this input also delays insertion of

training patterns after MaxT so that bursts are not

interrupted.

■

Units are in bytes. Supports M to 1,024 bytes in

increments of M, where M equals 16 or 32 bytes

depending on the Atlantic buffer width.

ctl_td_burstlimit[10:0]

Input

Sets the maximum burst size to be sent by the

transmitter. A control word is inserted at the end of

the burst limit. Burst limit values are restricted to

multiples of burst unit size (set via

ctl_td_burstlen[9:0]

), and depending on other

transmitter parameters, the values may be limited to

a minimum value. You can use IP Toolbench to

determine the valid values (set Parameter Type to

Fixed Value to determine the valid values, and then

set back to Real Time Programmable). The units are

in bytes.

Table 5–8. Data Path and Control Status (Part 2 of 2)

Signal

Direction

Clock Domain

Description