Altera POS-PHY Level 4 IP Core User Manual

Page 16

2–6

Chapter 2: Getting Started

Files Generated for Altera IP Cores (Legacy Parameter Editor)

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

Files Generated for Altera IP Cores (Legacy Parameter Editor)

The Quartus II software version 14.0 and previous parameter editor generates the

following output file structure for Altera IP cores:

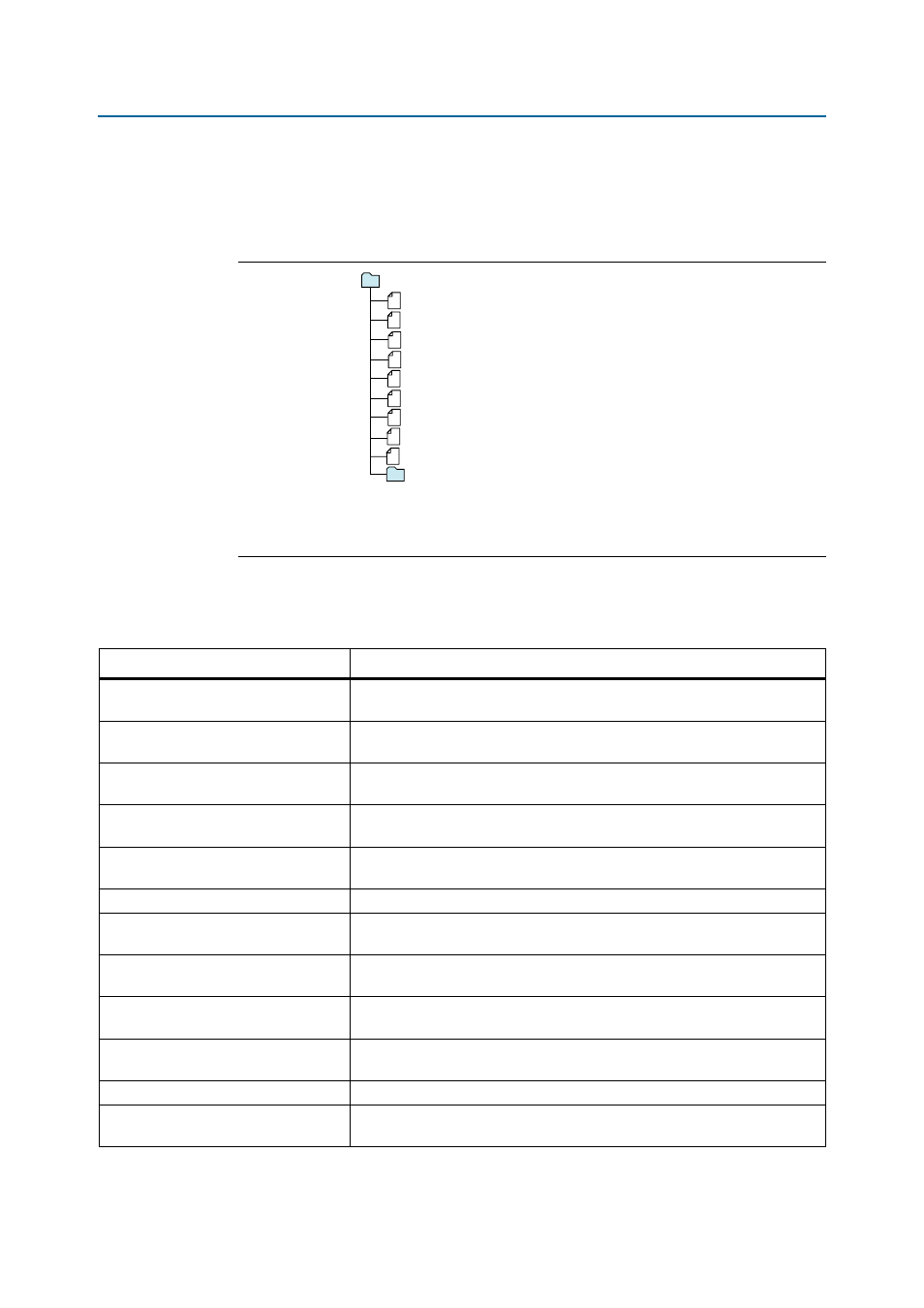

Figure 2–5. IP Core Generated Files (Legacy Parameter Editor)

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

<Project Directory>

<your_ip>.html - IP core generation report

<your_ip>_testbench.v or .vhd - Testbench file

1

<your_ip>.bsf - Block symbol schematic file

<your_ip>_syn.v or .vhd - Timing & resource estimation netlist1

<your_ip>_bb - Verilog HDL black box EDA synthesis file

<your_ip>.vo or .vho - IP functional simulation model 2

<your_ip>.qip - Quartus II IP integration file

<your_ip>.v or .vhd - Top-level HDL IP variation definition

<your_ip>_block_period_stim.txt - Testbench simulation data

1

Table 2–1. Generated Files (Part 1 of 2)

File

Description

<variation name>_atlfifo_concat.v

An encrypted HDL file for Quartus II synthesis. This file is automatically added

to your Quartus II project. You should not modify this file.

<variation name>_dpa_concat.v

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

<variation

name>_pl4_rx_core_constraints.tcl

Constraint settings file for Quartus II synthesis. Use this file to specify

constraints required to achieve performance requirements.

<variation name>_refresh_model.tcl

A Tcl script that regenerates the IP functional simulation model, in both Verilog

HDL (.vo) and VHDL (.vho) formats.

<variation name>_run_modelsim.tcl

A Tcl script that automates the process of running the testbench with the IP

functional simulation model.

<variation name>_rx_data_proc.ocp

An OpenCore Plus file, for time limited or tethered hardware evaluation.

<variation name>_rx_modules.v

An encrypted HDL file for Quartus II synthesis. This file is automatically added

to your Quartus II project. You should not modify this file.

<variation

name>_rx_data_phy_altlvds.v

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

<variation name>_rx_core.v

A generated HDL file for Quartus II synthesis. This file is automatically added to

your Quartus II project. You should not modify this file.

<

variation name>_syn.v or

<

variation name>_syn.vhd

A timing and resource netlist for use in some third-party synthesis tools.

<variation name>_tb.v

A Verilog HDL testbench for the requested parameterization.

<variation name>.bsf

Quartus II symbol file for the IP core variation. You can use this file in the

Quartus II block diagram editor.