Altera POS-PHY Level 4 IP Core User Manual

Page 31

Chapter 3: Parameter Settings

3–11

Optional Features

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

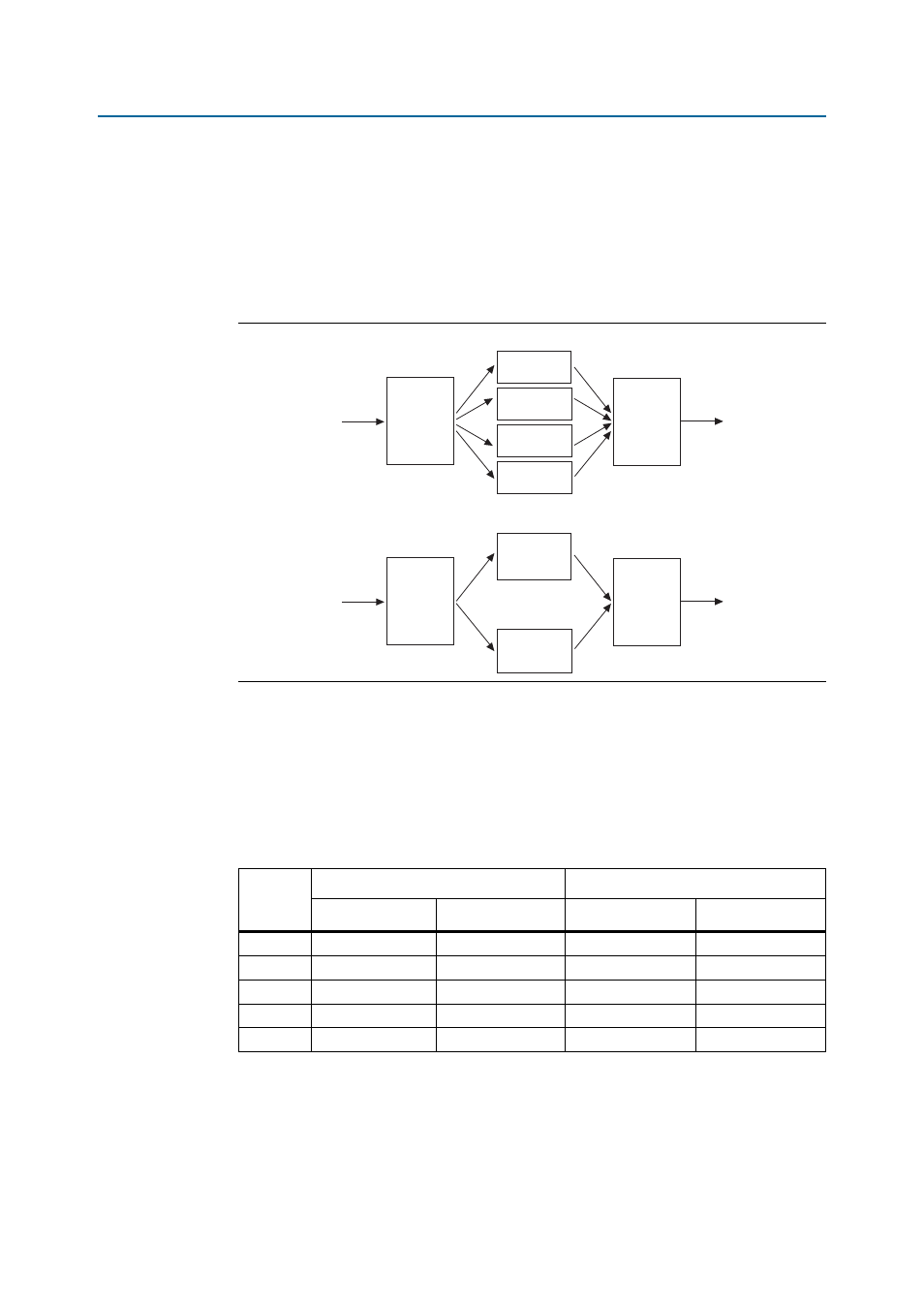

Each FIFO RAM block is implemented independently in the available device memory

(for example, with M512, M4K, or M9K blocks) and each device memory has a fixed

number of available configurations. The FIFO RAM block depth for small buffer

configurations (such as 128 × 36 of M4K memory) can be smaller than the minimum

configurable depth of the memory element, meaning that the remainder of the

memory is wasted. By using 2 FIFO RAM blocks instead of 4 you may get better

memory utilization.

Figure 3–3

shows the comparison of FIFO RAM blocks.

Both FIFO buffer width and FIFO buffer size affect memory utilization. The

improvement for a two block FIFO buffer configuration versus a four block FIFO

buffer configuration ranges from half the memory consumption for small buffers, to

the same memory consumption for large buffers.

Table 3–5

gives a comparison of the memory utilization for a Stratix II device with 4

FIFO RAM blocks versus 2 FIFO RAM blocks.

Figure 3–3. Comparison of FIFO RAM Blocks

Table 3–5. Memory Utilization Comparison

(Note 1)

Buffer

Size

(bytes)

Atlantic Interface Width 32

Atlantic Interface Width 64

2 FIFO RAM Blocks 4 FIFO RAM Blocks

2 FIFO RAM Blocks

4 FIFO RAM Blocks

512

4 M4K

4 M4K + 4 M512

4 M4K + 2 M512

8 M4K + 4 M512

1,024

4 M4K

8 M4K

6 M4K

8 M4K + 4 M512

2,048

6 M4K

8 M4K

6 M4K

12 M4K

4,096

12 M4K

12 M4K

10 M4K

12 M4K

8,192

24 M4K

24 M4K

20 M4K

20 M4K

Note to

Table 3–5

:

(1) Stratix II device, receive (Rx), shared buffer, data path width 32, parity enabled.

Read Side

FIFO Block 0

(size = fifo_size/4)

Write Side

FIFO Block 1

(size = fifo_size/4)

FIFO Block 2

(size = fifo_size/4)

FIFO Block 3

(size = fifo_size/4)

Read Side

FIFO Block 0

(size = fifo_size/2)

Write Side

FIFO Block 1

(size = fifo_size/2)

4 FIFO RAM Blocks

2 FIFO RAM Blocks