Avalon-mm interface register map, Avalon – Altera POS-PHY Level 4 IP Core User Manual

Page 66

4–28

Chapter 4: Functional Description—Receiver

Avalon-MM Interface Register Map

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

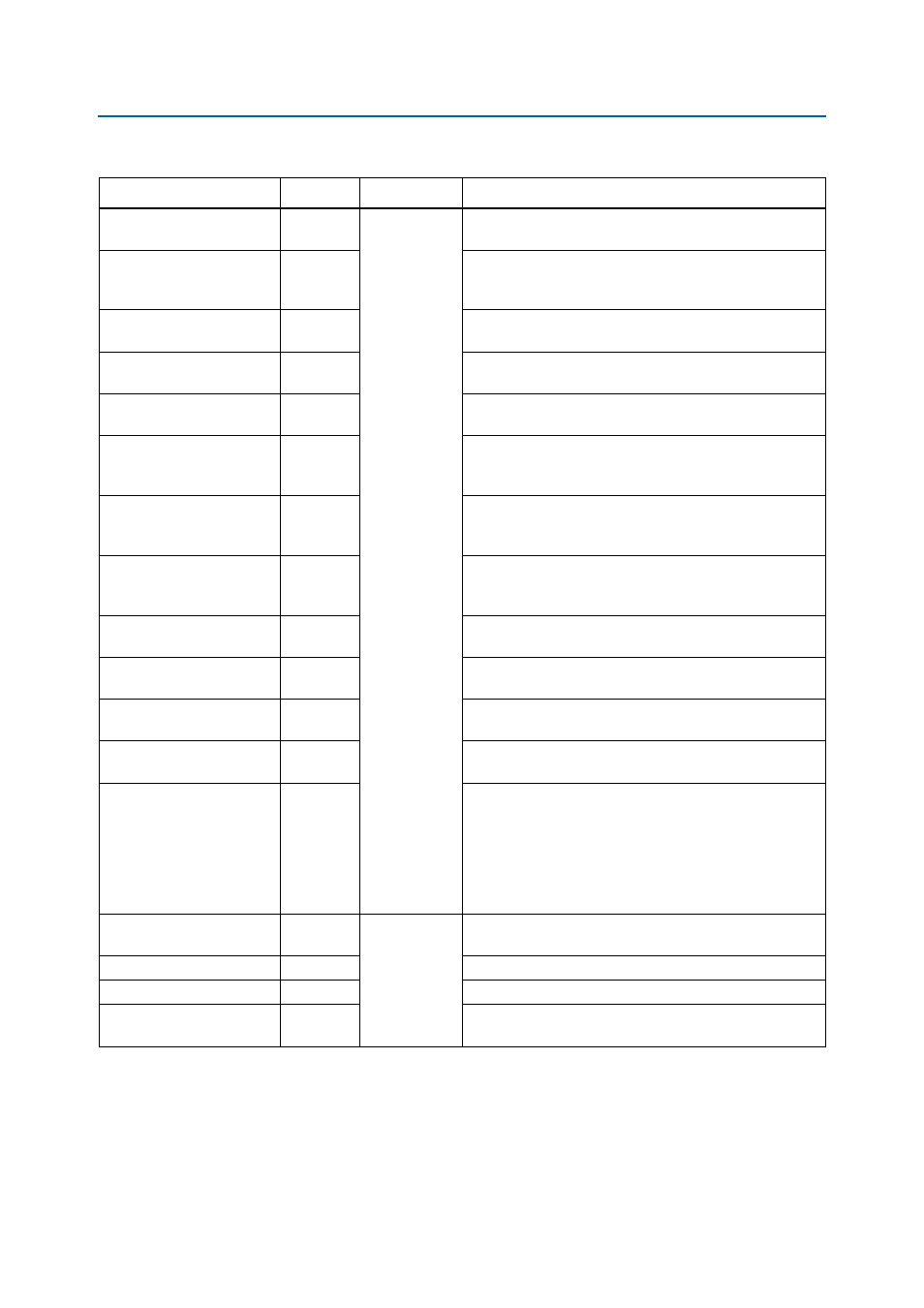

Avalon-MM Interface Register Map

Table 4–12

lists the Avalon-MM interface registers.

Table 4–11. Data Path Control and Status

Signal

Direction

Clock Domain

Description

stat_rd_rdat_sync

Output

rdint_clk

Main receiver data path sync output signal. Combination of

DPA, channel aligner sync, and DIP-4 status.

stat_rd_tp_flag

Output

Indicates that the receiver has detected a training pattern.

This signal is for debug purposes only. It does not indicate

that the data path is deskewed.

stat_rd_rsv_cw

Output

Indicates that the receiver has detected a reserved control

word. This signal is provided for information purposes only.

ctl_rd_dip4_good_

threshold[3:0]

Input

Number of consecutive correct DIP-4s to clear

stat_rd_dip4_oos

. Only change at reset.

ctl_rd_dip4_bad_

threshold[3:0]

Input

Number of consecutive DIP-4 errors to set

stat_rd_dip4_oos

. Only change at reset.

stat_rd_dip4_oos

Output

Receiver’s out-of-service flag. When asserted, the IP core is

still passing data, but is receiving DIP-4 errors above a

threshold.

err_rd_dip4

Output

Each clock cycle asserted indicates that one or more

(depending on the data path width parameter) calculated

DIP-4 values did not match the received DIP-4 values.

err_rd_pr

Output

Indicates that the receiver has detected a miscellaneous

protocol error. These errors correspond to invalid state

transitions in the data path state machine.

err_rd_tp

Output

Indicates that the receiver has detected an error in the

training pattern.

err_rd_sob

Output

Indicates that the receiver has detected a data burst that

does not start on a payload control word.

err_rd_sop8

Output

SOP violation. Two SOPs occurred less than eight rdat

cycles apart.

err_rd_abuf_oflw

Output

Indicates that an internal buffer has overflowed and data has

been lost.

ctl_rd_abuf_flush

Input

Flushes an internal buffer. While asserted, no data is written

to the Atlantic buffer(s). Data continues to be lost until

deasserted. The ctl_rd_abuf_flush signal must be

asserted for one rdint_clk cycle only, and any subsequent

assertion has to be done after minimum of approximately 20

cycles, because some ABUF internal signals are sent from

one clock domain to another.

err_rd_eightn

Output

rdint_clk

Indicates that the receiver has detected a burst that was not

a multiple of 16 bytes.

err_ry_paddr

Output

Invalid address received.

err_rd_eop_abort

Output

Indicates that the receiver has detected an EOP Abort.

err_rd_pad_byte_

non_zero

Output

Indicates that the receiver has detected an odd-sized burst

(in bytes), and the invalid pad byte was not zero.