Altera POS-PHY Level 4 IP Core User Manual

Page 105

Chapter 6: Testbench

6–7

Transmitter Testbench Description

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

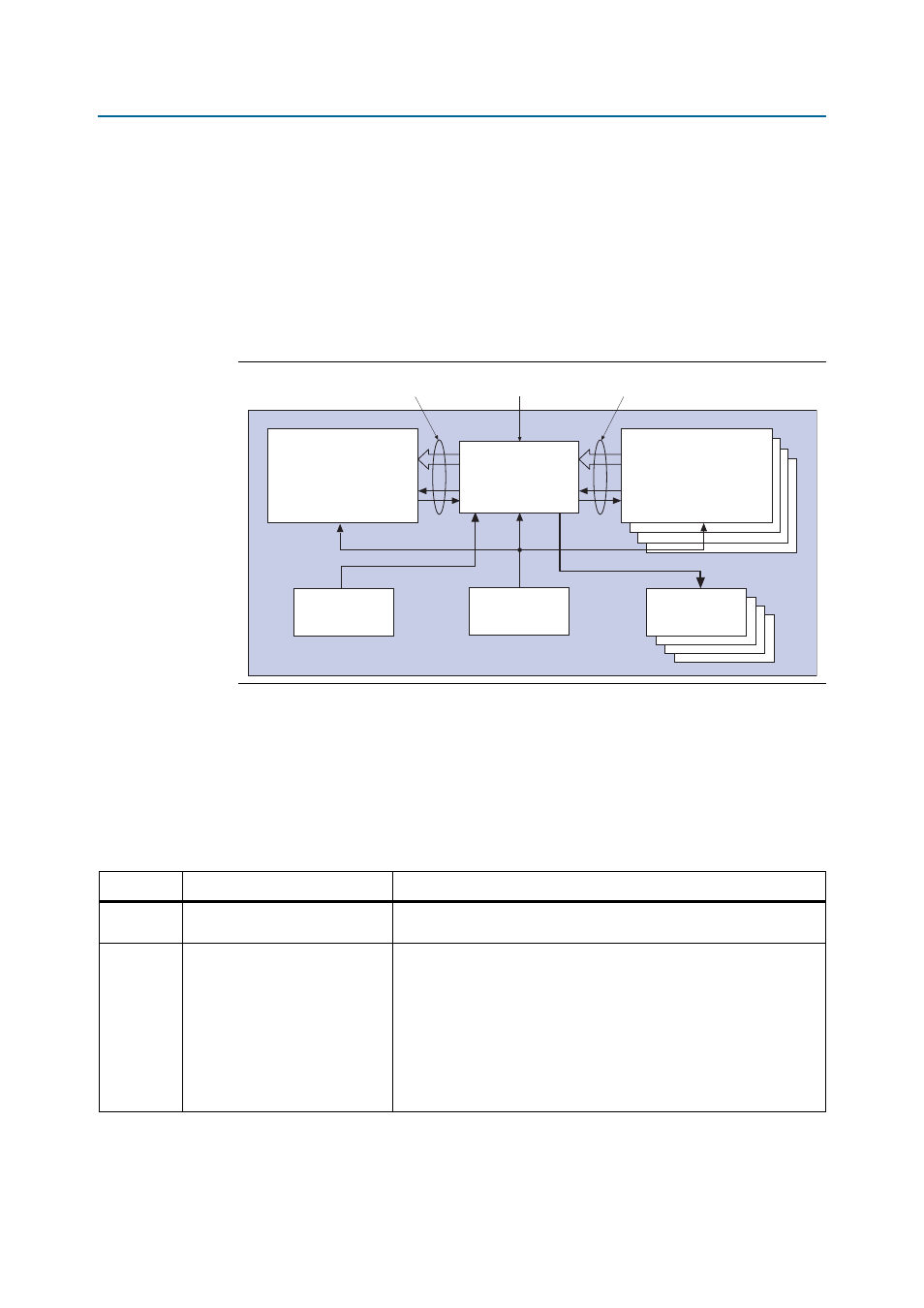

The testbench consists of three basic modules: data generator, user transmitter

variation, and packet analyzer. All testbench modules are in the <variation name>_tb.v

file. The testbench also consists of multiple support modules for pin monitoring, clock

generation, SPI-4.2 state machine tracking, and reset generation (refer to

Figure 6–2 on

page 6–7

). The data generator module consists of one Atlantic generator per port.

Each generator creates packets for a single port, via Verilog HDL tasks. These packets

are received by the user’s transmitter variation, which processes the packets and

converts them to SPI-4.2 bus format. Finally, the packet analyzer module receives the

data from the SPI-4.2 interface and verifies the data is correct.

Framing is asserted from the packet analyzer module’s status channel going to the

POS-PHY Level 4 transmitter IP core, which asserts the training pattern

(16'h0fff,16'hf000) until the receiver is synchronized. When the synchronization is

complete, the data generator module begins sending data.

During the main test the data generator module sends data to each port using Verilog

HDL tasks.

Table 6–5

summarizes the tasks that send data.

Figure 6–2. Transmitter Testbench

Packet Analyzer

POS-PHY Level 4

Atlantic Interface

Data Generator

(one per port)

Clock

Generator

Pin Monitor

Reset

SPI-4.2

Interface

Device Under Test

Atlantic

Interface

Transmitter

Variation

POS-PHY

Level 4

Table 6–5. Training Pattern Commands

Command

Format

Description

Pause

sapgen.portN.pause;

This command pauses a given port. No data is sent to a paused port. N is

the port number to pause.

Data Packet

sapgen.portN.pkt (length,

packet number, error);

N

is the port to which the data packet is sent.

length

is the number in bytes of the data pattern.

packet number

is a user-supplied number that identifies the packet.

error

generates an error on the Atlantic interface.

The error value can be:

■

0: No error.

■

1: Assert Atlantic error, set header error bit.