Status processor – Altera POS-PHY Level 4 IP Core User Manual

Page 76

5–6

Chapter 5: Functional Description—Transmitter

Block Description

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

For 32-bit (quarter-rate) variations, an ALTDDIO IP core serializes the tdclk, tdat,

and tctl lines.

Status Processor

The transmitter IP core monitors and decodes the tstat status channel from the

receiver. It handles framing, checking for DIP-2 errors, and extracting status. The

status is provided to the transmit scheduler if present, and is always available to the

user logic. The clock edge on which the transmitter samples the status channel is

programmable.

The re-timed optimistic/pessimistic filtered status appears on the following signals:

■

ctl_ty_extstat_val

: asserted when the following two signals are valid

■

ctl_ty_extstat_adr

: port

■

ctl_ty_extstat

: status

These signals are synchronous with the positive edge of txsys_clk. The txsys_clk

must be faster than the status clock, tsclk.

Based on the received status channel, these signals are updated when the finite state

machine is not in disable state. It is up to the user logic to ensure these signals are

used when stat_ts_sync is asserted.

In the individual buffers mode, if these signals are not connected to the user logic, the

Quartus II software removes the status FIFO buffer (tx_stat_fifo_user).

Given a calendar slot number, the status processor determines which port's status

belongs in the slot according to the calendar that it stores. When Asymmetric Port

Support

is turned off, the port number corresponds with the slot number (that is, slot

one is port one, and so on). When Asymmetric Port Support is turned on, a

programmable calendar is stored in memory, and the port corresponding to the slot is

looked up.

1

If the Asymmetric Port Support parameter is turned on, the Avalon

®

Memory-

Mapped (Avalon-MM) registers must be programmed prior to releasing the rsfrm bit

(refer to

“Avalon-MM Interface Register Map” on page 5–24

).

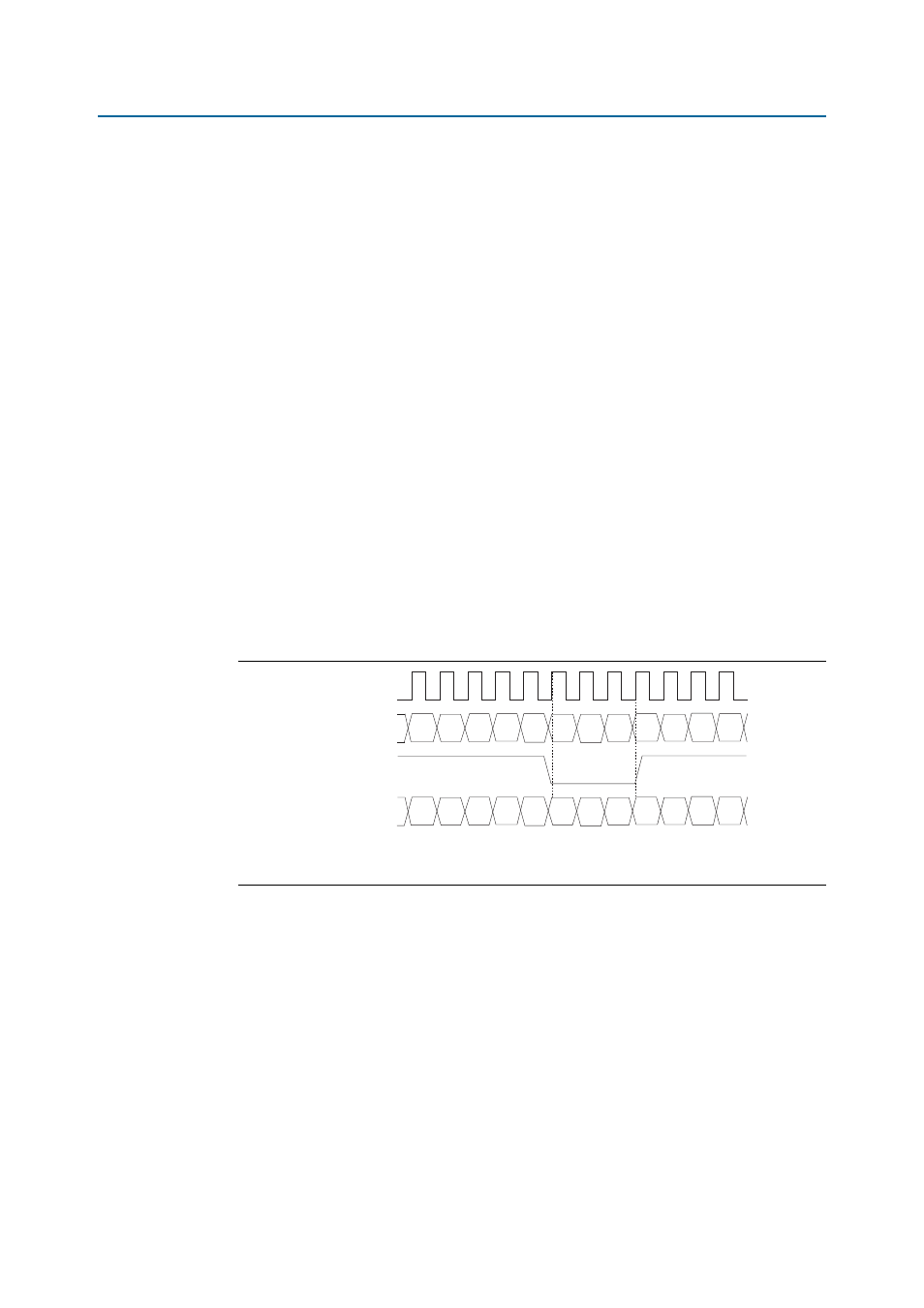

Figure 5–2. Transmitter Timing Diagram

Note to

Figure 5–2

:

(1) val is negated when the internal status FIFO buffer empties.

txsys_clk

stat_ty_extstat

stat_ty_extstat_val

stat_ty_extstat_adr

2'b00 2'b00 2'b00 2'b00 2'b01 2'bxx 2'bxx 2'bxx 2'b01 2'b00 2'b10

8'd0

8'd1

8'd2

8'd3

8'd4

8'dx

8'dx

8'dx

8'd5

8'd6

8'd7

2'b10

8'd0