Altera POS-PHY Level 4 IP Core User Manual

Page 135

Appendix G: Conversion from v2.2.x

G–5

Transmitter Signals

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

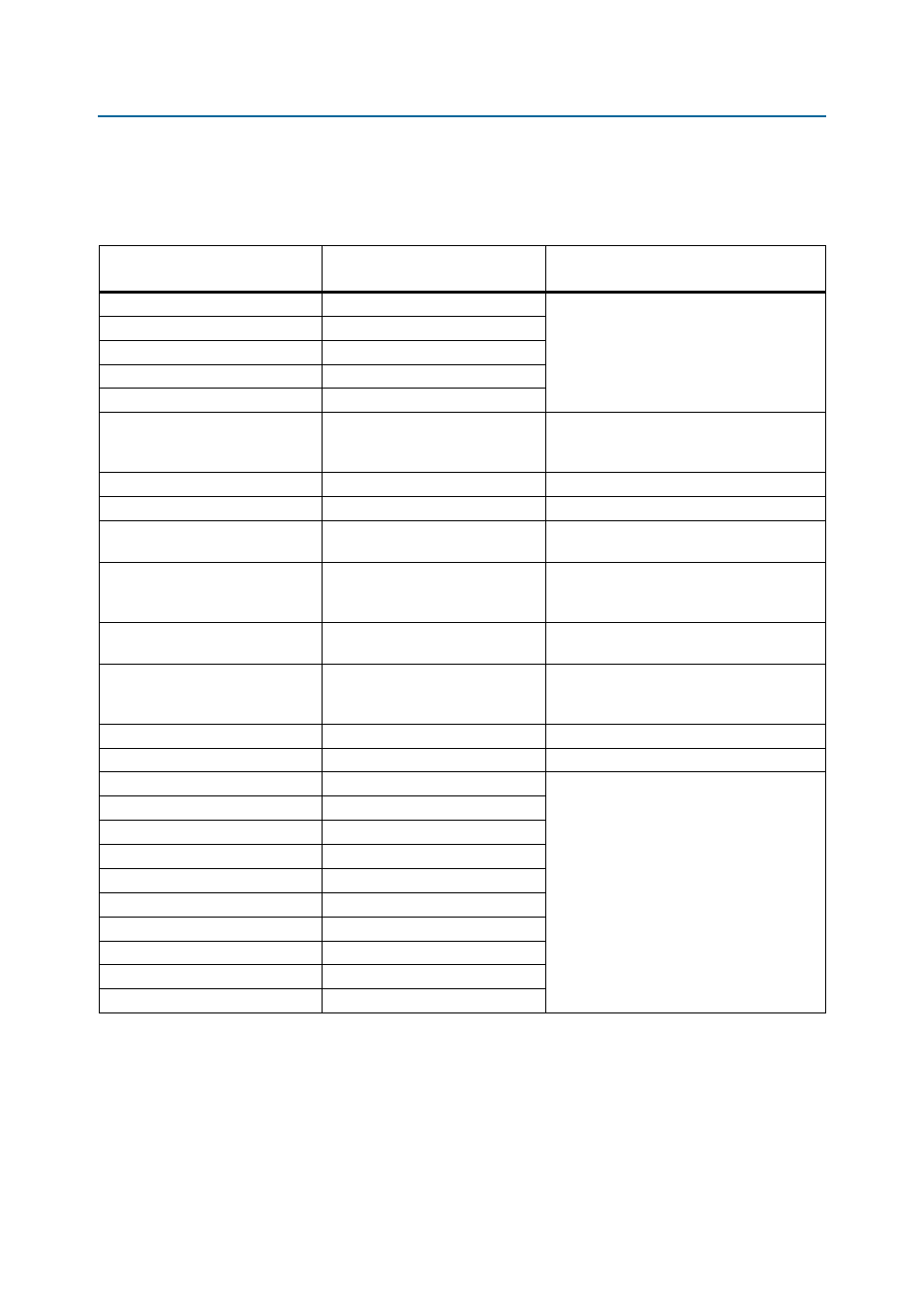

Table G–2

shows the new 2.4.x and v2.3.x transmitter signal names as they exist in the

top-level file, their equivalent v2.2.x signal names (if applicable), and notes explaining

the changes.

Table G–2. Transmitter Signal Changes (Part 1 of 3)

Version 2.4.x and 2.3.x Signal

Name

Version 2.2.x Signal Name

Notes

tdclk

tdclk

No change.

tctl

tctl

tdat[15:0]

tdat[15:0]

tsclk

tsclk

tstat[1:0]

tstat[1:0]

tsreset_n

–

New. Tied high in the IP Toolbench top-level

file. Refer to

for usage.

trefclk

trefclk

No change.

stat_tx_pll_locked

–

New signal indicating PLL lock.

tdint_clk

tx_coreclock

Derived from trefclk. Signals synchronous

to this clock are infixed by _td_.

tdint_reset_n

–

New. Tied high in the IP Toolbench top-level

file. Refer to

for usage.

txsys_clk

–

Signals synchronous to this clock are infixed

by _ty_.

txsys_reset_n

–

New. Tied high in the IP Toolbench top-level

file. Refer to

for usage.

txreset_n

txreset_n

No change. Resets all domains.

txinfo_aot[12:0]

txinfo_aot[15:0]

Change in port width.

aN_atxclk

aN_atxclk

No change

aN_atxreset_n

aN_atxreset_n

aN_atxdav

aN_atxdav

aN_atxena

aN_atxena

aN_atxdat

aN_atxdat

aN_atxsop

aN_atxsop

aN_atxeop

aN_atxeop

aN_atxmty

aN_atxmty

aN_atxerr

aN_atxerr

aN_atxadr

aN_atxadr