Spi-4.2 protocol errors – Altera POS-PHY Level 4 IP Core User Manual

Page 51

Chapter 4: Functional Description—Receiver

4–13

Error Flagging and Handling

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

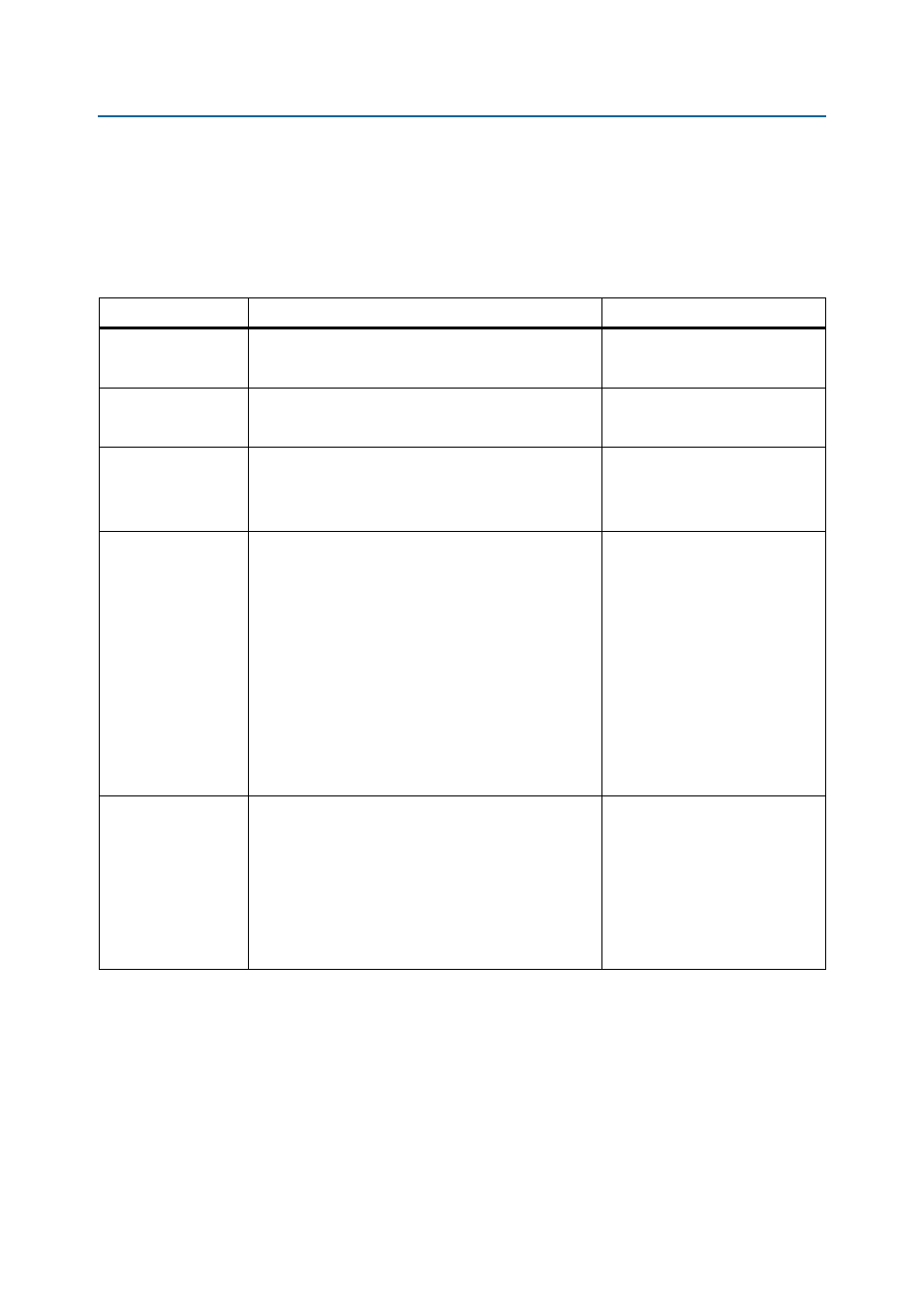

SPI-4.2 Protocol Errors

The receiver IP core decodes the control words from the incoming SPI-4.2 interface

and ensures that they follow the state machine shown in Fig. 6.2. Data Path State

Diagram of the SPI-4.2 Specification, and ensures that there are no other errors.

Table 4–3

summarizes the SPI-4.2 protocol errors.

Table 4–3. SPI-4.2 Protocol Error Handling (Part 1 of 3)

(Note 1)

,

Error

Condition

Response

Protocol error

A transition on the receiver data path that does not follow

Fig. 6.2. Data Path State Diagram of the SPI-4.2

Specification.

■

Assert err_rd_pr for one clock

cycle.

Start-of-packet spacing

violation (SOP8)

The SPI-4.2 specification states that SOP control words

should not be less than 8 cycles apart.

■

Asserts err_rd_sop8 for one

clock cycle. When this happens,

the data is not affected.

Start of burst error

(SOB)

Data or training data is received without a payload control

word.

■

Assert err_rd_sob for one

cycle.

■

Data is dropped until a proper

payload control word is received.

Training pattern error

Training pattern errors (err_rd_tp) occur when one of the

following conditions occur:

■

Training control portion is too short.

■

Training control portion is too long.

■

Training data portion is too short.

■

Training data portion is too long.

■

Training control word is followed by something other

than another training control word or training data

word.

■

Malformed data bus during a data or control word.

■

Missing IDLE before training pattern begins. (The IDLE

can be an EOP).

■

Assert err_rd_tp at the end of

the training pattern.

■

Channel aligner may not lock.

■

Some training pattern errors may

result in successive assertions of

the err_rd_tp interrupt (for

example, Training Control portion

> 10 cycles).

8N boundary error

(8N_ERR)

A burst that is neither a multiple of 16 bytes, nor an EOP.

■

Assert err_rd_eightn for one

clock cycle.

■

Packet is marked as errored.

■

Consider error as a missing EOP.

■

Cleanly terminate packet

internally as an EOP-Abort.

■

Process subsequent bursts as

per missing SOP.