Altera POS-PHY Level 4 IP Core User Manual

Page 64

4–26

Chapter 4: Functional Description—Receiver

Signals

POS-PHY Level 4 IP Core User Guide

December 2014

Altera Corporation

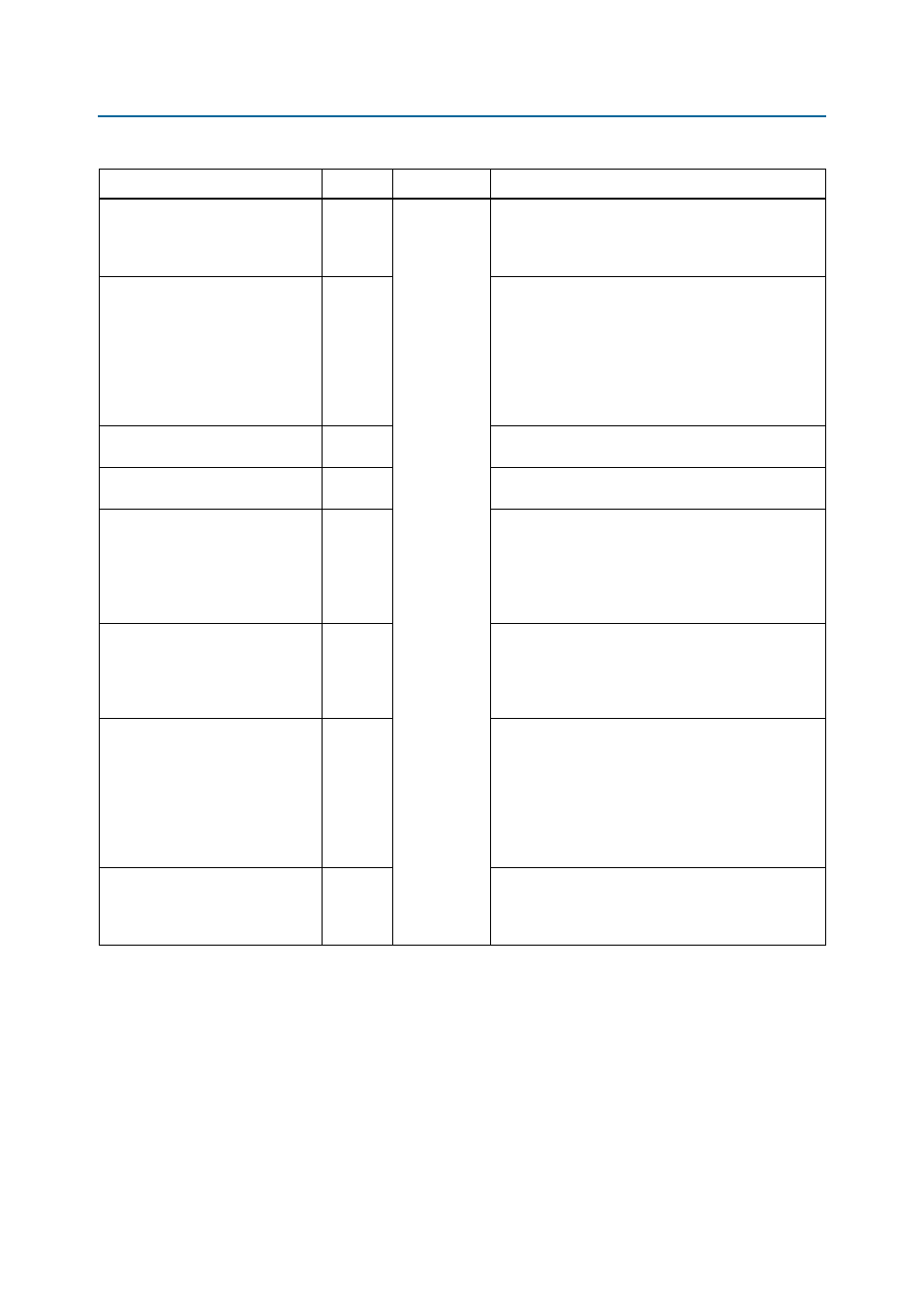

ctl_ry_rsfrm

Input

rxsys_clk

When asserted, the ctl_ry_rsfrm signal forces the

receiver status channel into framing mode beginning at

the end of the next frame. You can use ctl_ry_rsfrm

to indicate that the receiver requires retraining.

ctl_ry_dip2err_ins

Input

If you assert ctl_ry_dip2err_ins while it is

calculating the DIP2, it inverts it. It does not invert the

statuses on the way and does not wait for the end of the

calendar to do the inversion. Also, if the error is set for

the calendar length (plus 2 cycles, 1 for DIP2 one for

FRM), it is only active on one DIP2 calculation.

Therefore you should not see two consecutive DIP2

errors.

stat_ry_disabled

Output

Indicates that the calendar state machine is disabled,

and is transmitting continuous framing.

stat_ry_dip2state

Output

Indicates that the calendar state machine is in DIP-2

state.

err_ry_stat_fifo

Output

Indicates that the status FIFO buffer has underflowed or

overflowed causing the status finite state machine to go

into continuous framing state (refer to

). If the status FIFO buffer regularly

underflows or overflows, ensure the clock relationships

meet Altera guidelines.

ctl_ry_callen[7:0]

Input

Sets the length of the calendar in the outgoing status

frame. Zero is interpreted as 256. This port is absent if

asymmetric port support is turned on. Only change at

reset, or when ctl_ry_rsfrm and

stat_ry_disabled

are both asserted.

ctl_ry_calm[7:0]

Input

Sets the number of status calendar repetitions between

framing and DIP-2 in the outgoing status frame. If

err_ry_stat_fifo

is asserted, you need to increase

the number of repetitions. Refer to

. Zero is interpreted as 256. This port is

absent if asymmetric port support is turned on. Only

change at reset, or when ctl_ry_rsfrm and

stat_ry_disabled

are both asserted.

stat_ry_calsel

Output

Indicates the currently selected calendar when hitless

bandwidth reprovisioning is enabled. It is set to zero

otherwise. This port is absent if asymmetric port

support is turned off.

Table 4–9. SPI-4.2 Channel Control and Status (Part 2 of 3)

Signal

Direction

Clock Domain

Description