Functional description—transmitter, Features, Block description – Altera POS-PHY Level 4 IP Core User Manual

Page 71

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

5. Functional Description—Transmitter

The POS-PHY Level 4 IP core consists of the main SPI-4.2 processing logic, and one of

two first-in first-out (FIFO) buffer options: a single shared buffer with embedded

addressing and support for external scheduling, or an individual buffer for each port

including a full scheduler.

When the POS-PHY Level 4 IP core is configured as a transmitter, data flows from the

Atlantic

™

interface to the SPI-4.2 interface.

Features

■

Sends data packets on the SPI-4.2 interface

■

Inserts control words

■

Generates DIP-4

■

Inserts training sequence

■

Manages the FIFO buffer status

Block Description

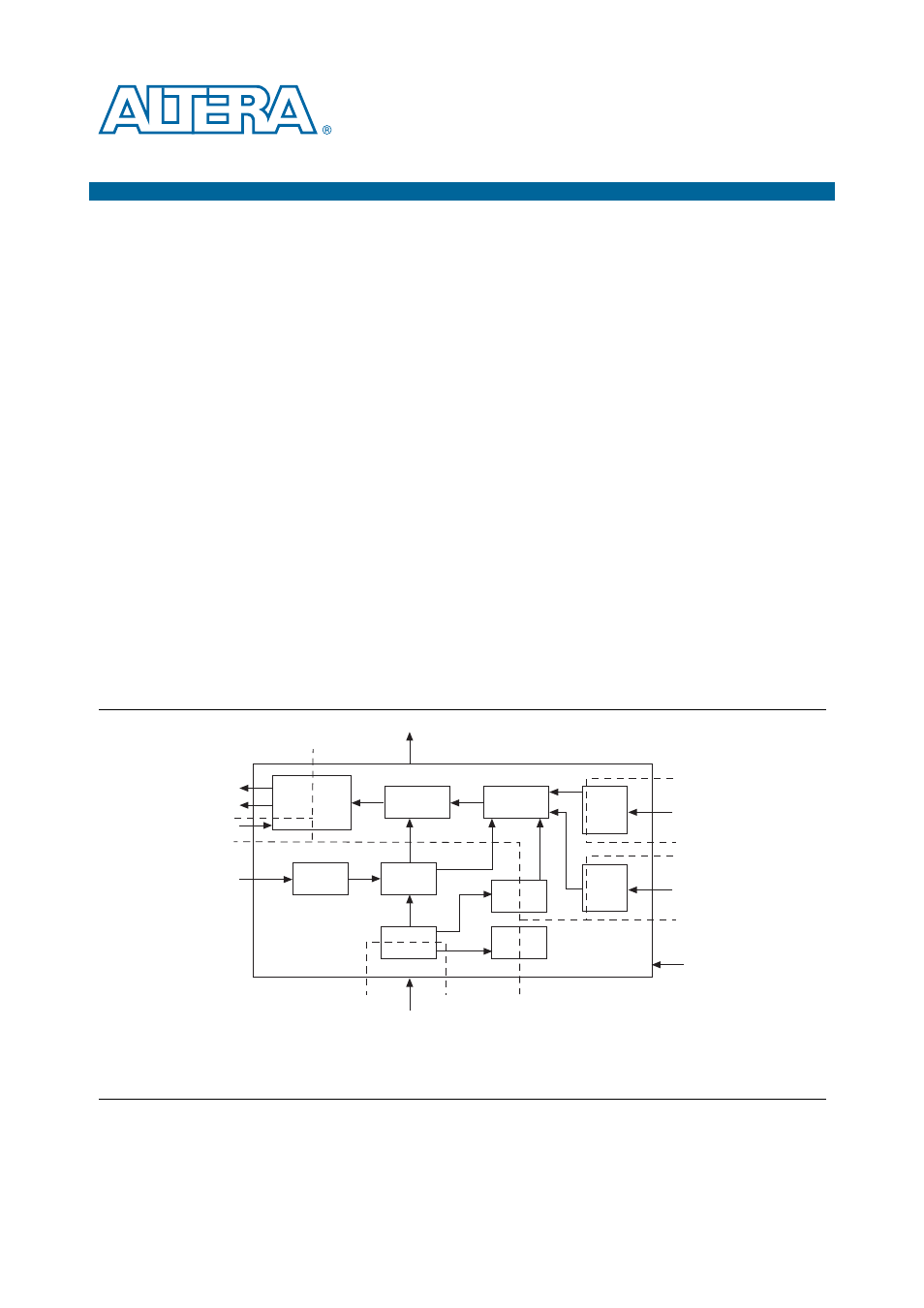

Figure 5–1 on page 5–1

shows the blocks and clocks that comprise the transmitter IP

core.

This section describes the top-level blocks of the POS-PHY Level 4 transmitter IP core.

Figure 5–1. Block Diagram—Transmitter

Notes to

Figure 5–1

:

(1) The dotted lines illustrate the clock domain separations.

(2) These blocks and signals are only present when the individual buffers mode is selected.

Parallel-to-Serial

Converter

Scheduler

(Note 2)

Status PHY

Status FSM

Status

Register

Scheduler

FIFO Buffer

User FIFO

Buffer

Data

Processor

Atlantic

Buffer 0

Atlantic

Interface 0

SPI4.2

Interface

tdclk

trefclk

txsys_clk

tdint_clk

rav_clk

tsclk

Atlantic

Buffer N

(Note 2)

Atlantic

Interface N