Altera POS-PHY Level 4 IP Core User Manual

Page 53

Chapter 4: Functional Description—Receiver

4–15

Error Flagging and Handling

December 2014

Altera Corporation

POS-PHY Level 4 IP Core User Guide

When you use DPA, the protocol checker block does not function until the DPA is

locked.

The latency from an error occurring on the SPI-4.2 interface to the assertion of the

corresponding error signal is unspecified.

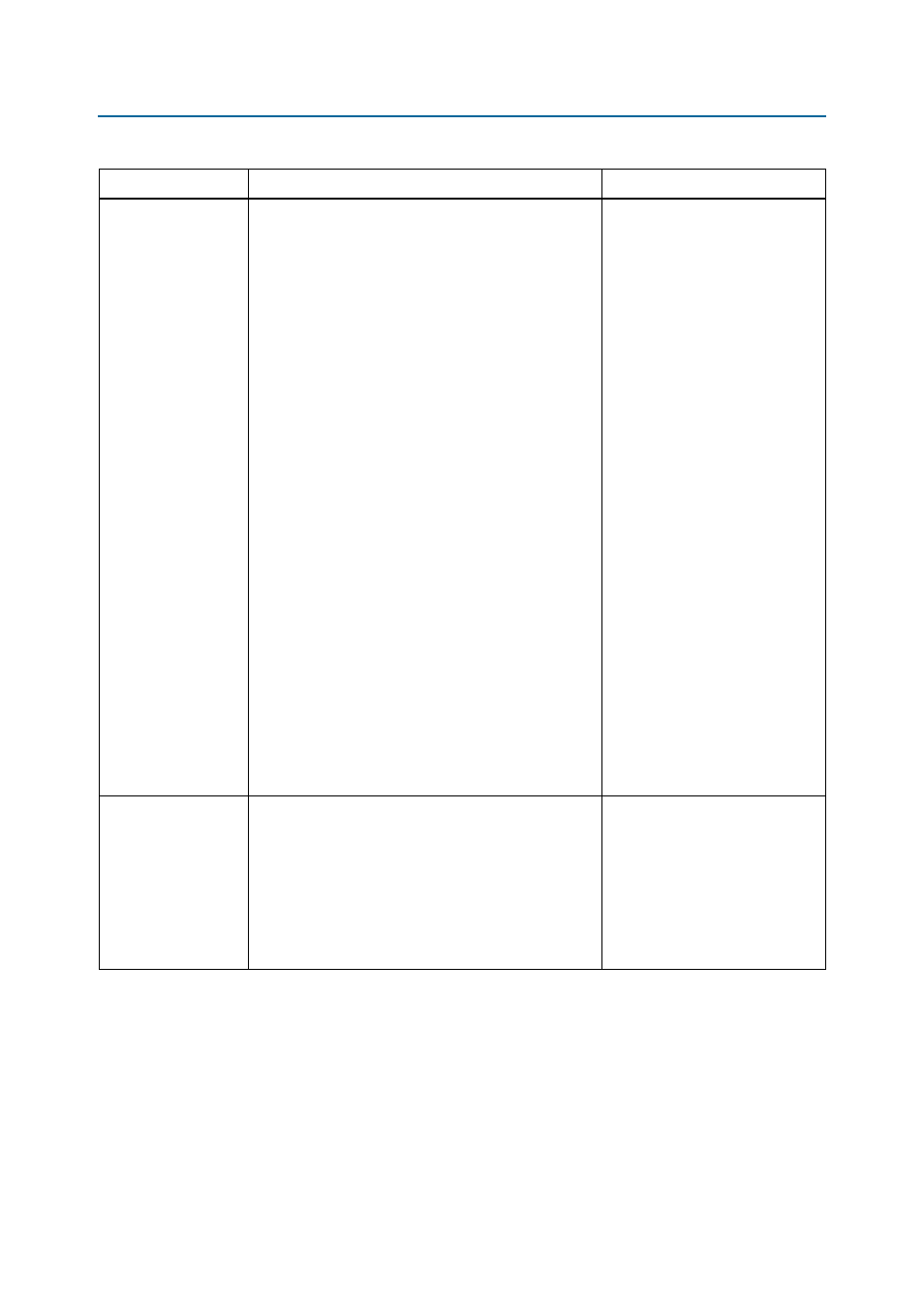

Burst of DIP-4 errors

Data bus out of alignment (consecutive DIP-4 errors over a

programmable threshold)

■

IP core asserts

stat_rd_dip4_oos

when a

bad_level

of consecutive DIP-4

errors are detected (Refer to

“DIP-4 Out of Service Indication”

on page 4–17

).

■

Control input signal is provided

(ctl_ry_rsfrm) for you to force

the receiver status channel logic

to cease proper calendar framing

and send continuous 2’b11

framing pattern. The transition

from proper calendar frame to

continuous framing occurs after

the current calendar frame is

completed.

■

The ctl_ry_rsfrm signal is

controlled externally by user logic

or software-controlled registers

to initiate automatic retraining.

■

Asserting the ctl_ry_rsfrm

signal does not affect the receiver

operation as a SPI-4.2 sink.

■

Any incoming SPI-4.2 traffic

continues to be processed as

usual.

■

Atlantic error checking is also

unaffected by the ctl_ry_rsfrm

signal.

Packet address error

A packet address error (err_ry_paddr) occurs when a

packet is received with an out-of-range port address.

■

Assert err_ry_paddr.

■

In the shared buffer with

embedded addressing mode, the

burst/packet is sent to the user

logic, and it is up to the user logic

to define and determine the

course of action. In the individual

buffers mode, the packet/burst is

discarded.

Notes to

Table 4–3

:

(1) More than one error of the same type may occur per internal clock. In such a case, the error is only asserted once.

(2) DIP-4 errors and protocol errors are independent.

(3) Injection of the EOP-Abort may cause a missing SOP error to occur in the Atlantic FIFO buffer (if error checking is turned on).

Table 4–3. SPI-4.2 Protocol Error Handling (Part 3 of 3)

(Note 1)

,

(2)

Error

Condition

Response