Bus control – Zilog Z08470 User Manual

Page 95

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Direct Memory Access

Notes

:

* Address can increment (+) or decrement (-) from the programmed starting address (As), which is the first

address for transfer or search.

** Occurs only when the Ready line is still inactive just prior to the beginning of the last possible cycle in the

operation. For example, Ready is sampled inactive on the rising edge of CLK in the last cycle of the last read

operation.

*** Search only has no destination. Simultaneous transfer/search cannot have both ports variable. This class of

operation is programmed as a DMA search only operation, with variable addresses assigned to the

programmed source port. What the DMA senses as the source port may be either the real source or destination,

as determined by external hardware. See the 'Applications' chapter.

Bus Control

The DMA transfers and searches data by controlling the system buses in the

same way that the Z80 CPU controls them to perform read and write cycles.

Specifically, the DMA controls the following lines:

•

Address Bus (16 bits)

•

Data Bus (8 bits)

•

IORQ

•

MREQ

•

RD

•

WR

In addition, the DMA can also be programmed to watch a WAIT line

through its dual-purpose CE/WAIT pin.

Continuous

M

M**

M-1**

As

±(M**

***

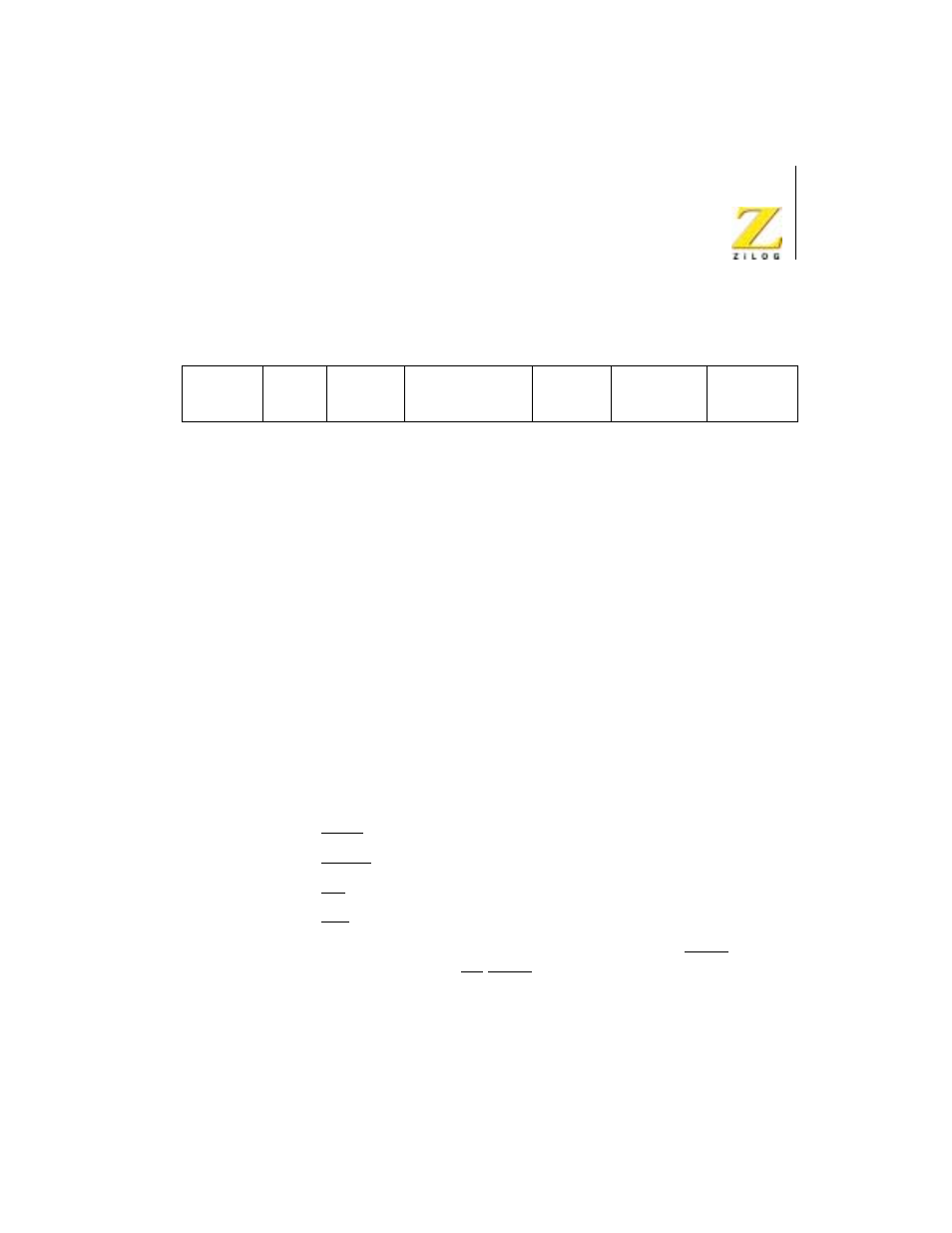

Table 12. Contents of Counters After DMA Stops Due to Byte Match (Search or Transfer/

Search Operations)

Class

Mode

Match Occurs

On This Byte

Bytes Transferred At Stop

If Transferring

Byte Counter

Source Port

Address Counter*

Destination Port

Address Counter