Daisy chain interrupt nesting, Figure 131. return from interrupt cycle timing – Zilog Z08470 User Manual

Page 328

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Serial Input/Output

308

The Tipple time of the interrupt daisy-chain, both the High-to-Low and

the Low-to-High transitions, limits the number of devices that can be

placed in the daisy-chain. Ripple time can be improved with carry-

lookahead, or by extending the interrupt acknowledge cycle.

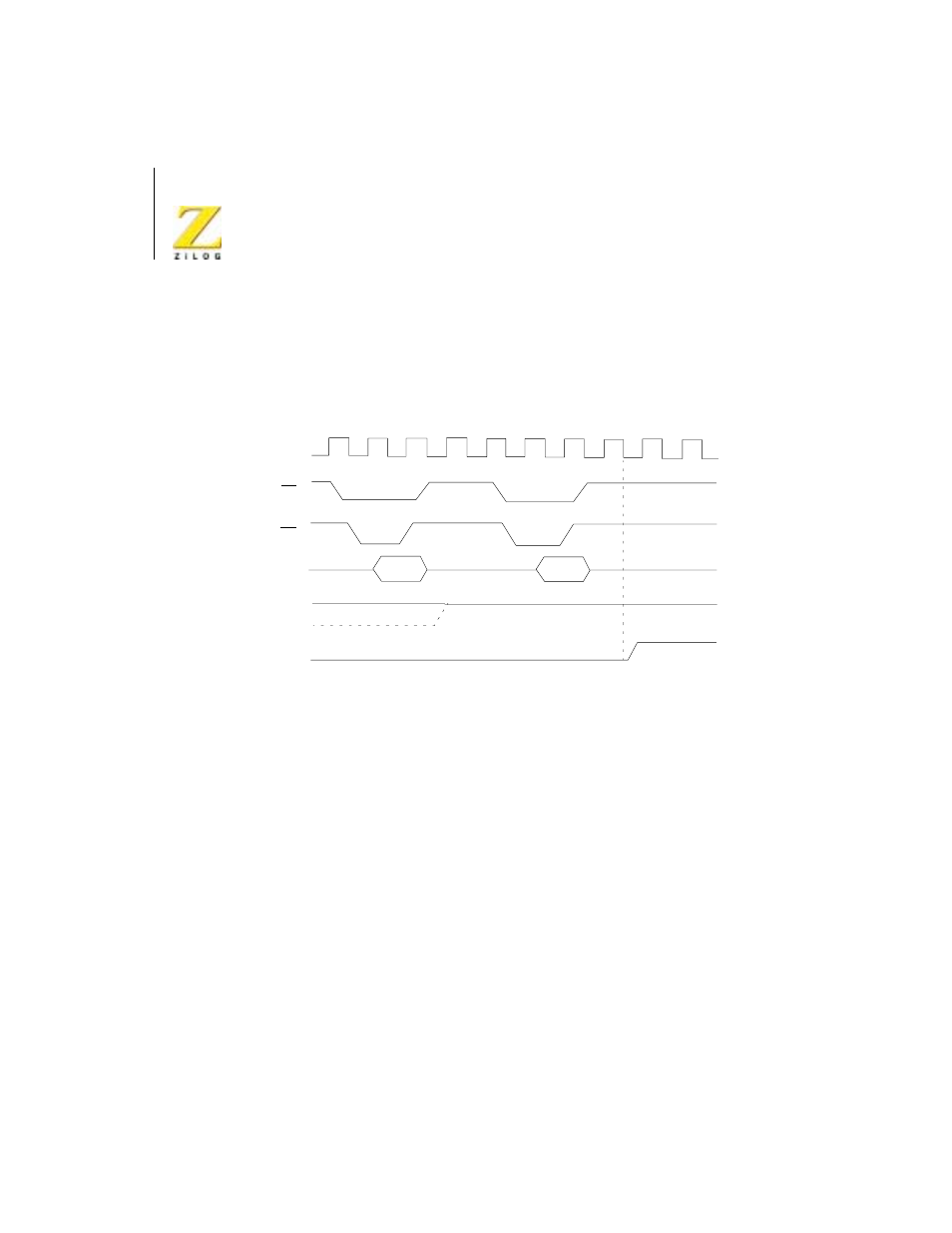

Figure 131. Return from Interrupt Cycle Timing

Daisy Chain Interrupt Nesting

Figure 132 illustrates the daisy-chain configuration of interrupt circuits and

their interaction with nested interrupts, which is an interrupt that is inter-

rupted by another with a higher priority.

Each box in the illustration can be a separate external Z80 peripheral circuit

with a user-defined order of interrupt priorities. However, a similar daisy-

chain structure also exists inside the Z80 SIO, which has six interrupt levels

with a fixed order of priorities.

The situation illustrated in Figure 132 occurs when the transmitter of

Channel B interrupts and is granted service. While this interrupt is being

serviced, it is interrupted by a higher priority interrupt from Channel A. The

second interrupt is serviced and, upon completion, a RETI instruction is

T

1

Φ

RD

M1

T

2

T

3

T

4

IEI

IEO

D7–D0

ED

4D

T

1

T

2

T

3

T

4

T

1