Figure 65. bus request and acceptance timing, Bus release byte-at-a-time – Zilog Z08470 User Manual

Page 178

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Direct Memory Access

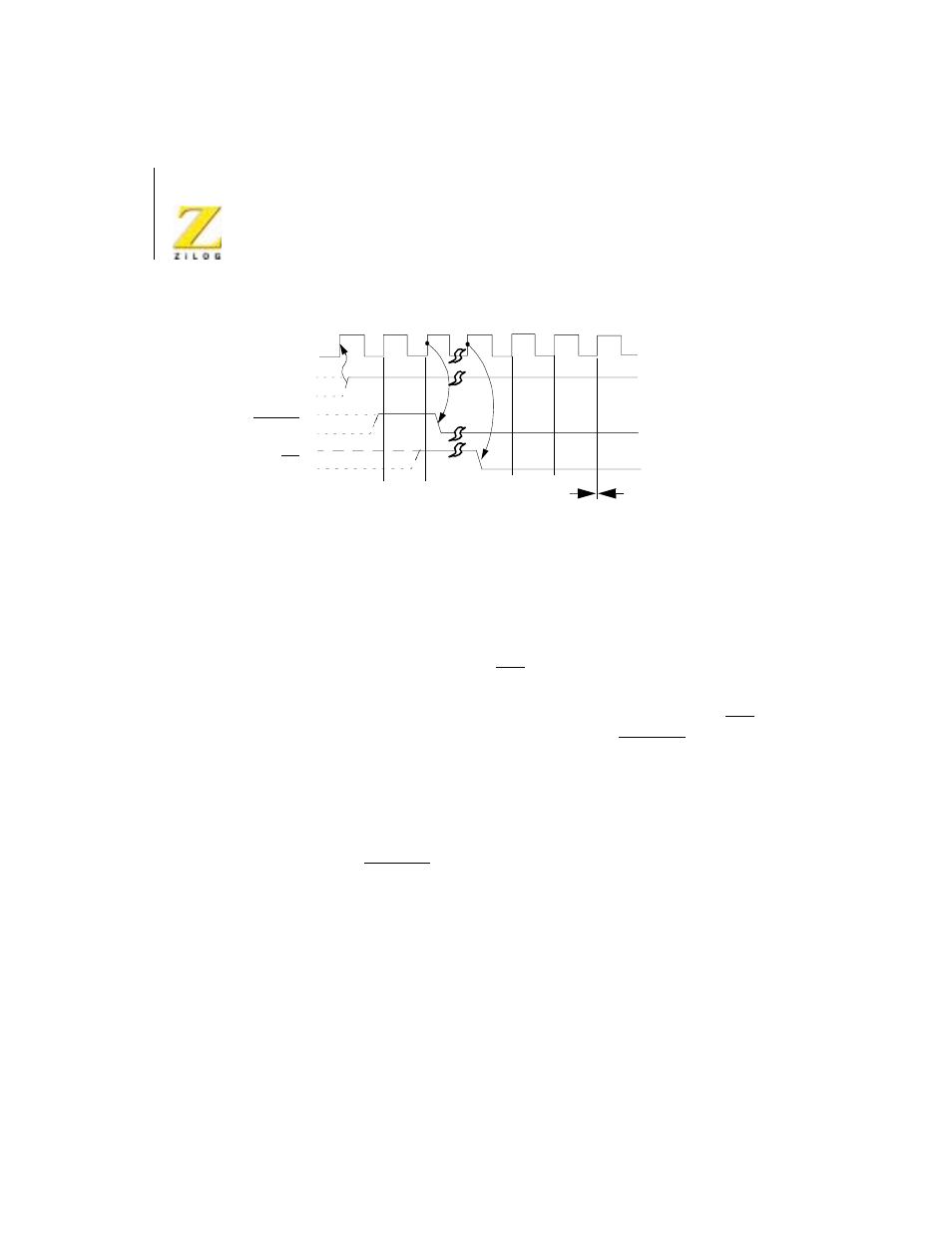

Figure 65.

Bus Request and Acceptance Timing

Continuous mode is the only instance when a pulse on RDY allows the

DMA to become bus master.In this event, the DMA becomes bus master

but does not begin operations.

When the DMA detects a Low on BAI for two consecutive rising edges of

CLK, the DMA begins transferring data on the next rising edge of CLK.

In Byte mode, after each byte is transferred, the DMA waits until its BAI

line goes inactive before requesting the bus again on BUSREQ for the next

byte transfer. This feature allows a minimum of one CPU machine cycle to

occur between each byte transferred.

Bus Release Byte-at-a-Time

In Byte mode, BUSREQ is brought High on the rising edge of CLK prior to

the end of each read cycle (search-only) or write cycle (transfer and trans-

fer/search) as illustrated in Figure 66. This action occurs regardless of the

state of RDY. There is no possibility of confusion when a Z80 CPU is used

because the CPU cannot begin an operation until the following clock cycle.

Nor does this condition affect most other CPUs. The result of timing is one-

clock-cycle less time needed for a byte transfer.

BUSREQ

RDY

Active

Inactive

DMA

Inactive

DMA

Active

BAI

CLK

Note: RDY is detected as a level, not an edge