< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

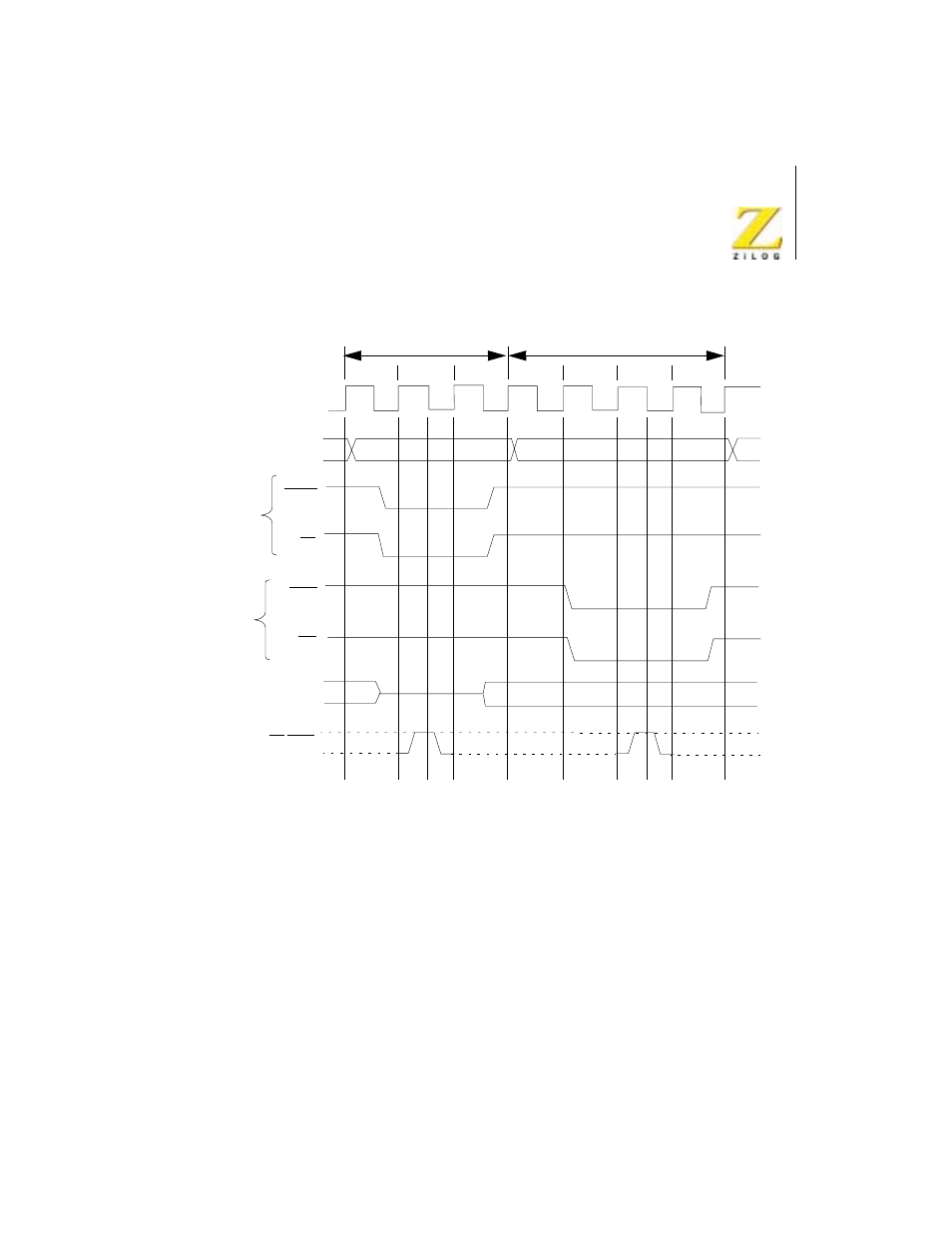

Direct Memory Access

Figure 61.Sequential Memory-to-I/O Transfer, Standard Timing (Searching is Optional)

CE/WAIT

D7–D0

Memory

Drive DMA

DMA Drives Data Bus

WR

IORQ

RD

MREQ

READ

WRITE

A15–A0

CLK

Memory Read

I/O Write

T

1

T

2

T

3

T

2

T

W

T

3

T

1