Write register 2 group, Write register 3 group, Figure 42. write register 2 group – Zilog Z08470 User Manual

Page 116

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Direct Memory Access

Write Register 2 Group

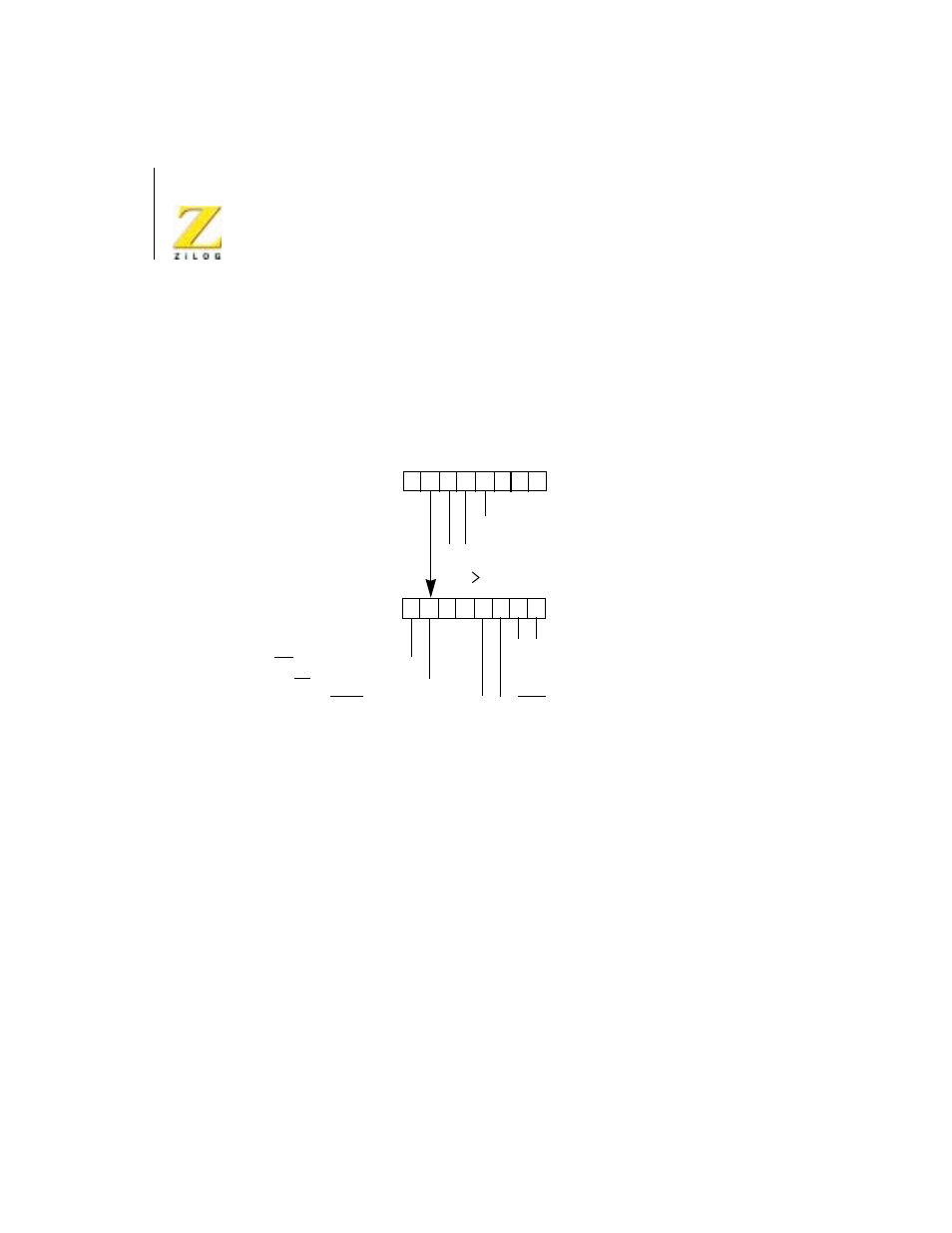

Bits 7, 2, 1, and 0, depicted in Figure 42, specify the base register byte for

this group. The group is used only when Port B is used, for example, do not

program it for a search-only, simultaneous transfer, or simultaneous

transfer/search with Port A as the source. Its syntax is the same as WR1.

Figure 42.

Write Register 2 Group

Write Register 3 Group

Bits 7, 1, and 0, depicted in Figure 43, specify the base register byte for this

group. The group is used primarily to specify the stop-on-match condition

as well as the specific match byte for a search operation. It can perform fast,

one-byte enabling of both bus requests and interrupts. A description of its

functions follows.

D7 D6 D5 D4 D3 D2 D1 D0

Base Register Byte

0

0

0

1

1

1

0

1

= Port B Address Decrements

0 = Port B is Memory

0 = Port B is I/O

Port B Variable

0

0

0

1

1

1

0

1

= Cycle Length = 3

= Cycle Length = 2

= Do Not Use

= Port B Address Increments

= Port B Address Fixed

Timing Byte

= Cycle Length = 4

WR Ends 1/2 Cycle Early = 0

RD Ends 1/2 Cycle Early = 0

MREQ Ends 1/2 Cycle Early = 0

0 = IORQ Ends 1/2 Cycle Early

0

0

0

0