Functional description, Figure 109. transmit and receive data path – Zilog Z08470 User Manual

Page 246

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Serial Input/Output

226

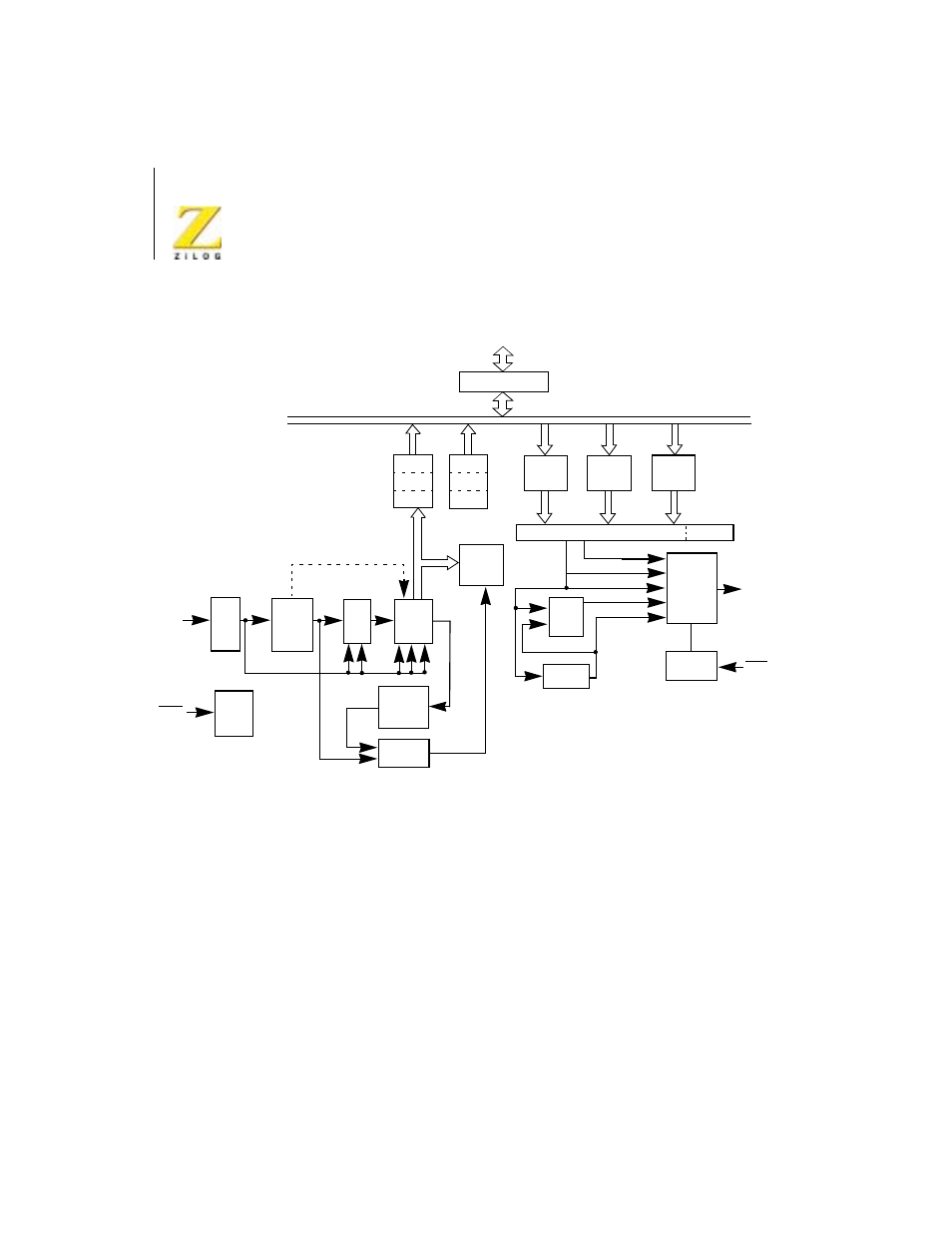

Figure 109. Transmit and Receive Data Path

Functional Description

The functional capabilities of the Z80 SIO are described in two ways: as a

data communications device, and as a Z80 family peripheral.

As a data communications device, The S80 SIO transmits and receives

serial data, and meets the requirements of various data communications

protocols. As a Z80 family peripheral, it interacts with the Z80 CPU and

other Z80 peripheral, circuits, and shares their data, address and control

Receive

Error

Logic

I/O Data Buffer

CPU I/O

Internal Data Bus

Receive

Clock

Logic

ASYNC Data

CRC Delay

Register

(8 Bits)

SYNC-

CRC

RxDA

RxCA

Hunt Mode (BISYNC)

3 Bits

1-Bit

Delay

CRC

Checker

SYNC

SDLC-CRC

CRC Result

SYNC-CRC

Transmit

Clock Logic

SYNC Data

SDLC-CRC

ASYNC Data

Transmit

Multiplexer

and

TxDA

TxCA

20-Bit Transmit Shift Register

Start Bit

Transmit

WR7

SYNC

and Zero

Delay

Register

WR6

SYNC

Register

Data

SDLC Data

CRC

Generator

2-Bit

Zero

(5 Bits)

Insert

Register

Delete

Receive

S.R.

(8 Bits)

Receive

Error

FIFO

Receive

Error

FIFO