Table 33, Write register 1, Table 34 – Zilog Z08470 User Manual

Page 297: Reset commands

Z80 CPU Peripherals

User Manual

UM008101-0601

Serial Input/Output

277

The Reset Transmit CRC Generator command normally initializes the CRC

generator to 0s. If the SDLC mode is selected, this command initializes the

CRC generator to 1s. The Receive CRC checker is also initialized to 1s for

the SDLC mode.

Write Register 1

WR1 (

) contains the control bits for the various interrupt and

Wait/Ready modes.

External/Status Interrupt Enable (D0)

The External/Status Interrupt Enable allows interrupts to occur as a result of

transitions on the DCD, CTS, or SYNC inputs, as a result of a Break/Abort

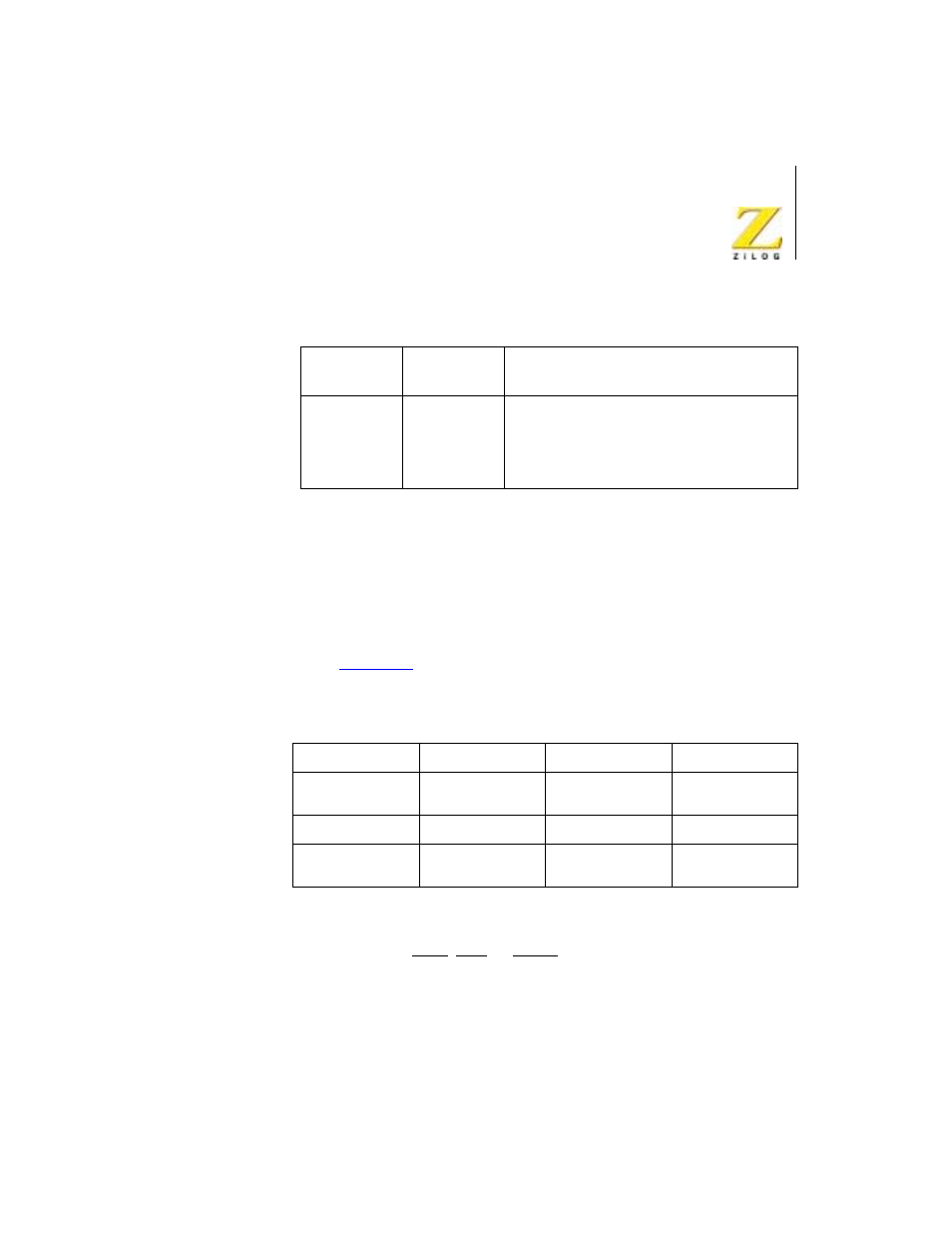

Table 14. Reset Commands

CRC Reset

Code 1

CRC Reset

Code 0

Result

0

0

Null Code (no affect)

0

1

Reset Receive CRC Checker

1

0

Reset Transmit CRC Generator

1

1

Reset Tx Underrun/End of Message latch

Table 15. Write Register 1

D7

D6

D5

D4

Wait/Ready

Enable

Wait or Ready

Function

Wait/Ready on

Receive Transmit

Receive Interrupt

Mode 1

D3

D2

D1

D0

Receive Interrupt

Mode 0

Status Affects

Vector

Transmit Interrupt

Enable

External Interrupts

Enable