Figure 16, Figure 16a, Figure 16b – Zilog Z08470 User Manual

Page 57: Figure 16c, Figure 16d

< %27 2GTKRJGTCNU

7UGT /CPWCN

UM008101-0601

Direct Memory Access

also requires external logic and inhibits memory refresh. Additionally, it

reduces DMA throughput.

All DMA transfers interrupt dynamic memory refresh by the CPU and

most of them idle the CPU. It is, therefore, important to consider these

implications when making the trade-off for higher DMA transfer speed.

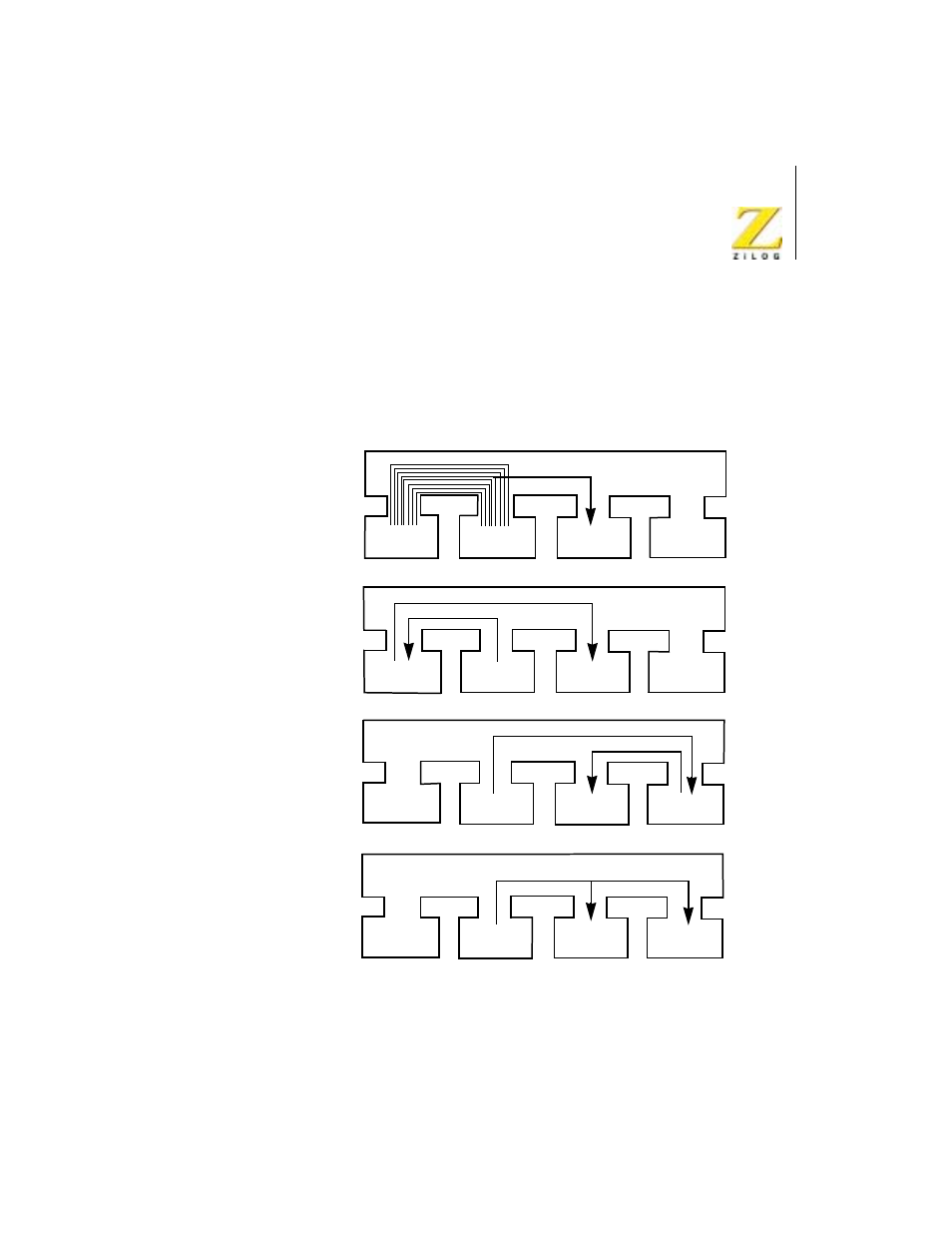

Figure 16.

Conceptual Comparison of Various I/O Transfer Methods

CPU

MEMORY

I/O

CPU

MEMORY

I/O

Read/Write Cycle

DMA

DMA

D.

DMA

Simultaneous

Transfers

C.

DMA

Sequential

Instruction

Read Cycle

Write Cycle

BUS

BUS

BUS

CPU

MEMORY

I/O

DMA

CPU

MEMORY

I/O

DMA

Fetch and Read Cycles

Write Cycle

BUS

B.

Z80/Z8000

Block Transfer

Instruction

A.

Conventional

Programmed

Instruction

Sequence

Write Cycle

Read Cycle