Altera ALTDQ_DQS2 User Manual

Page 98

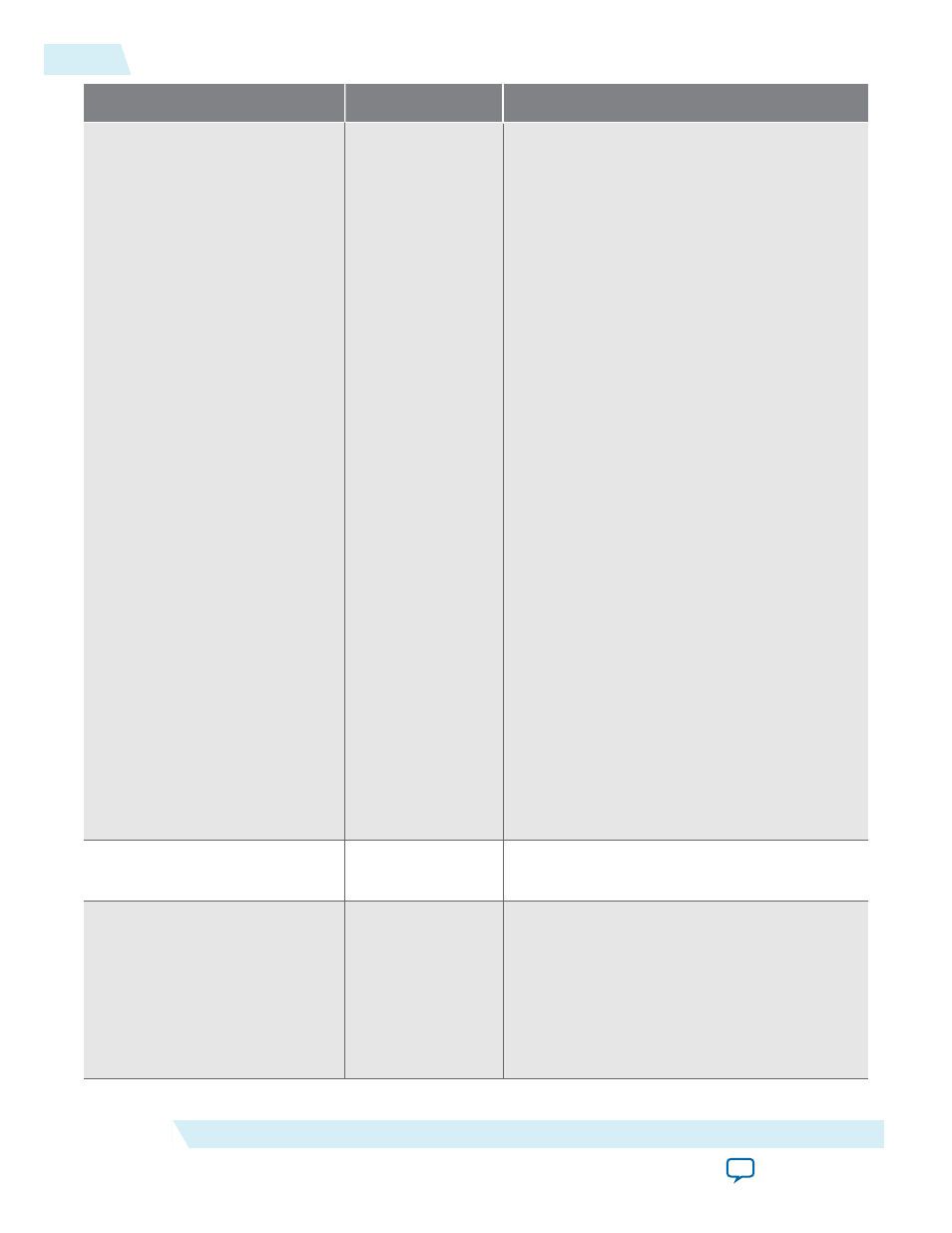

Date

Version

Changes

July 2014

2014.07.07

• Replaced MegaWizard Plug-In Manager

information with IP Catalog.

• Added standard information about

upgrading IP cores.

• Added standard installation and licensing

information.

• Clarified that configuration data must be

input in LSB first ordering and updated the

typical frequency for

config_clock_in

from

Reconfiguration for ALTDQ_DQS2

on

page 38 section.

that this signal is also supported in Stratix V

devices. Also clarified that the this signal is

1-bit wide for Stratix V devices and 2-bits

wide for Arria V and Cyclone V devices.

• Updated

,

, and

to update IOE delay settings information.

• Removed lfifo_rdata_en and lfifo_rdata_

valid ports information from

and

.

• Added information about checking the

validity of the data coming from the read

FIFO in

• Added

on page 77

and

on page 59

sections.

• Updated

Sequence for Arria V GZ and Stratix V

Block Bit Sequence for Arria V GZ and

on page 40 to include

Arria V GZ devices.

• Clarified that the ALTDQ_DQS2 does not

support DQS tracking.

January 2013

2.2

• Updated note in Figure 3–8 on page 3–10.

• Added “Additional Information” section.

December 2012

2.1

• Replaced previous design examples with the

following design examples:

• For Arria V devices: 12.1_AV_BasicDe‐

sign.qar

• For Stratix V devices: 12.1_SV_BasicDe‐

sign.qar

• Made necessary changes in the document to

reflect the design examples replacement.

98

Document Revision History

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide