Altera ALTDQ_DQS2 User Manual

Page 76

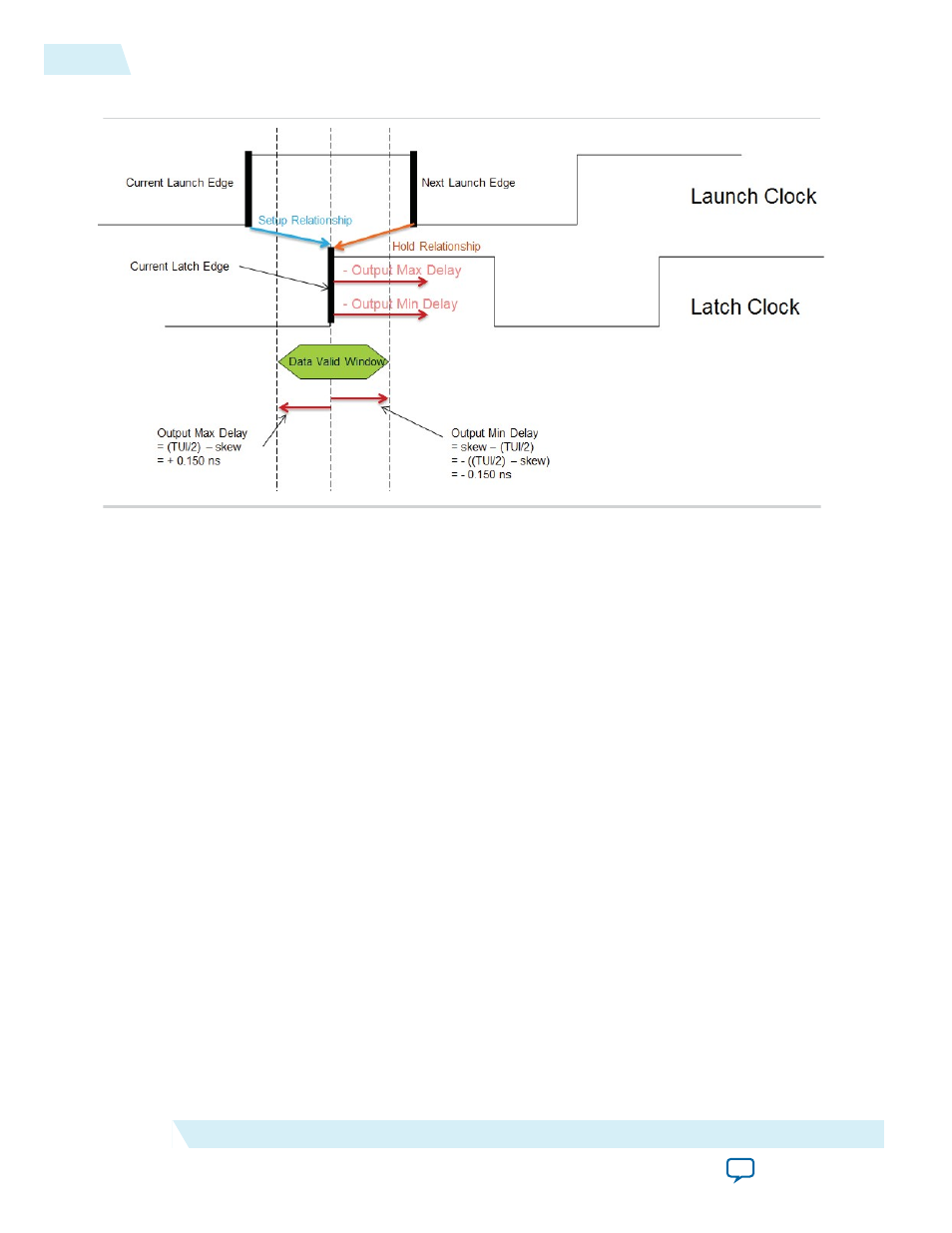

Figure 44:

The following

set_false_path

commands ensure that we are analyzing only the same edge

transfers, by removing the opposite edge transfers.

Note: These assignments are optional.

Example 5: set_false_path Commands

set_false_path -setup -rise_from [get_clocks{pll_inst/alterapll_inst/

altera_pll_i/general[2].gpll

�

PLL_OUTPUT_COUNTER/divclk}] -fall_to

[get_clocks{dqs_out}]

set_false_path -setup -fall_from [get_clocks{pll_inst/alterapll_inst/

altera_pll_i/general[2].gpll

�

PLL_OUTPUT_COUNTER/divclk}] -rise_to

[get_clocks{dqs_out}]

set_false_path -hold -rise_from [get_clocks{pll_inst/alterapll_inst/

altera_pll_i/general[2].gpll

�

PLL_OUTPUT_COUNTER/divclk}] -rise_to

[get_clocks{dqs_out}]

set_false_path -hold -fall_from [get_clocks{pll_inst/alterapll_inst/

altera_pll_i/general[2].gpll

�

PLL_OUTPUT_COUNTER/divclk}] -fall_to

[get_clocks{dqs_out}]

The following

set_multicycle_path

commands ensure that the correct transfer between the DDlO and

Read FlFO.

Example 6: set_multicycle_path Commands

set_multicycle_path -from {*/altdq_dqs2_stratixv:altdq_dqs2_inst/

input_path_gen[*].capture_reg

�

HIGH_DFF} -to {*/

76

Constraining Outgoing DQS Strobe

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide