Upgrading ip cores – Altera ALTDQ_DQS2 User Manual

Page 8

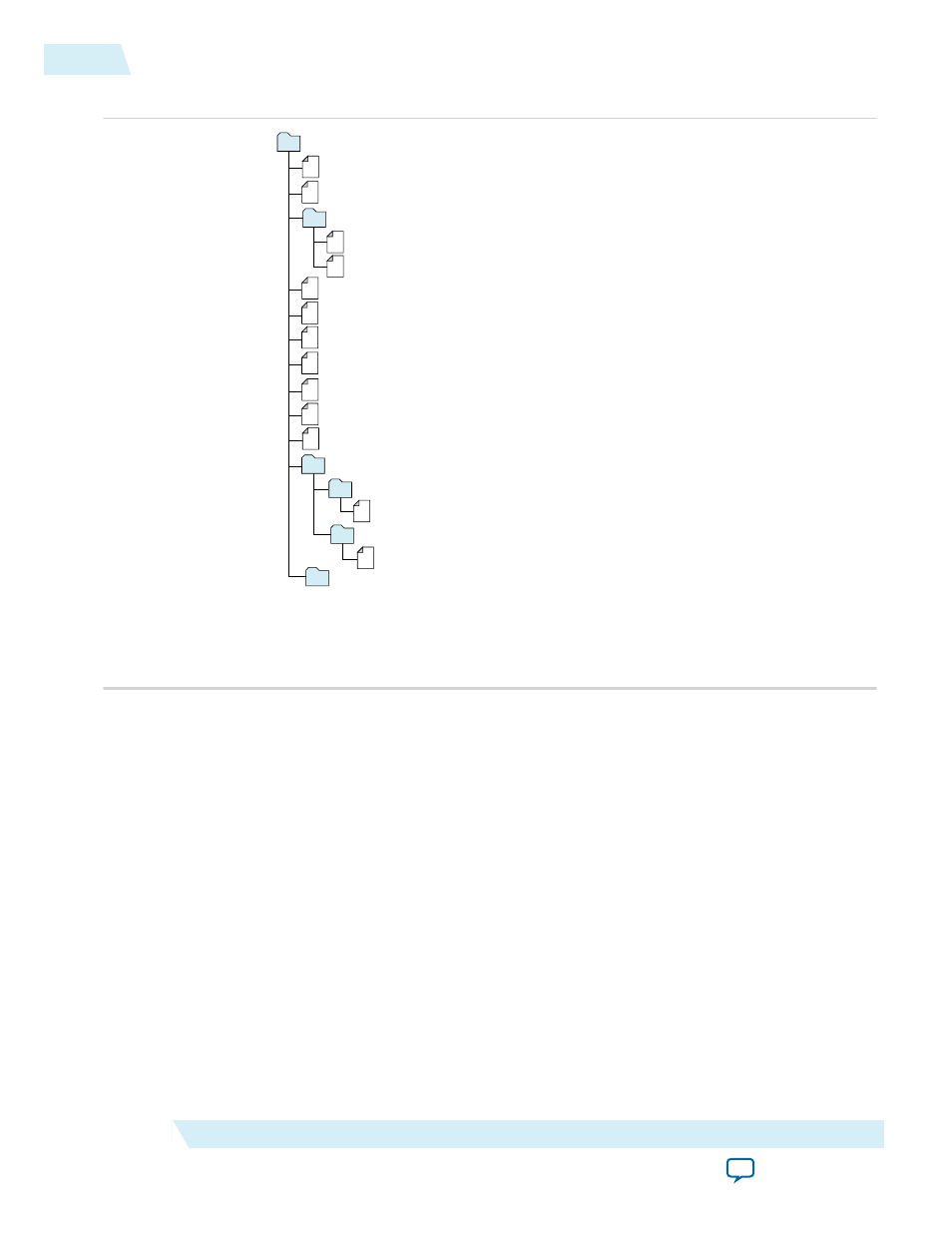

Figure 6: IP Core Generated Files

Notes:

1. If supported and enabled for your IP variation

2. If functional simulation models are generated

or _example

- Testbench or example1

1

1

Upgrading IP Cores

IP core variants generated with a previous version of the Quartus II software may require upgrading

before use in the current version of the Quartus II software. Click Project > Upgrade IP Components to

identify and upgrade IP core variants.

The Upgrade IP Components dialog box provides instructions when IP upgrade is required, optional, or

unsupported for specific IP cores in your design. You must upgrade IP cores that require it before you can

compile the IP variation in the current version of the Quartus II software. Many Altera IP cores support

automatic upgrade.

The upgrade process renames and preserves the existing variation file (

.v

, .

sv

, or

.vhd

) as

_

BAK.v

,

.sv

,

.vhd

in the project directory.

8

Upgrading IP Cores

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide