Dynamic reconfiguration for altdq_dqs2, Dynamic reconfigura, Tion for altdq_dqs2 – Altera ALTDQ_DQS2 User Manual

Page 38

Port name

Type

Width

Description

config_data_in

Input

1

Receives the serial configuration

data stream that shifts into the

serial-to-parallel shift registers.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

config_extra_io_ena[]

Input

m

Receives the clock enable signal

for the additional I/O configura‐

tion block.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

Note: For more information about the dynamic configuration blocks in Stratix V device, refer to “I/O

Configuration Block and DQS Configuration Block” in the

chapter of the Stratix V Device Handbook.

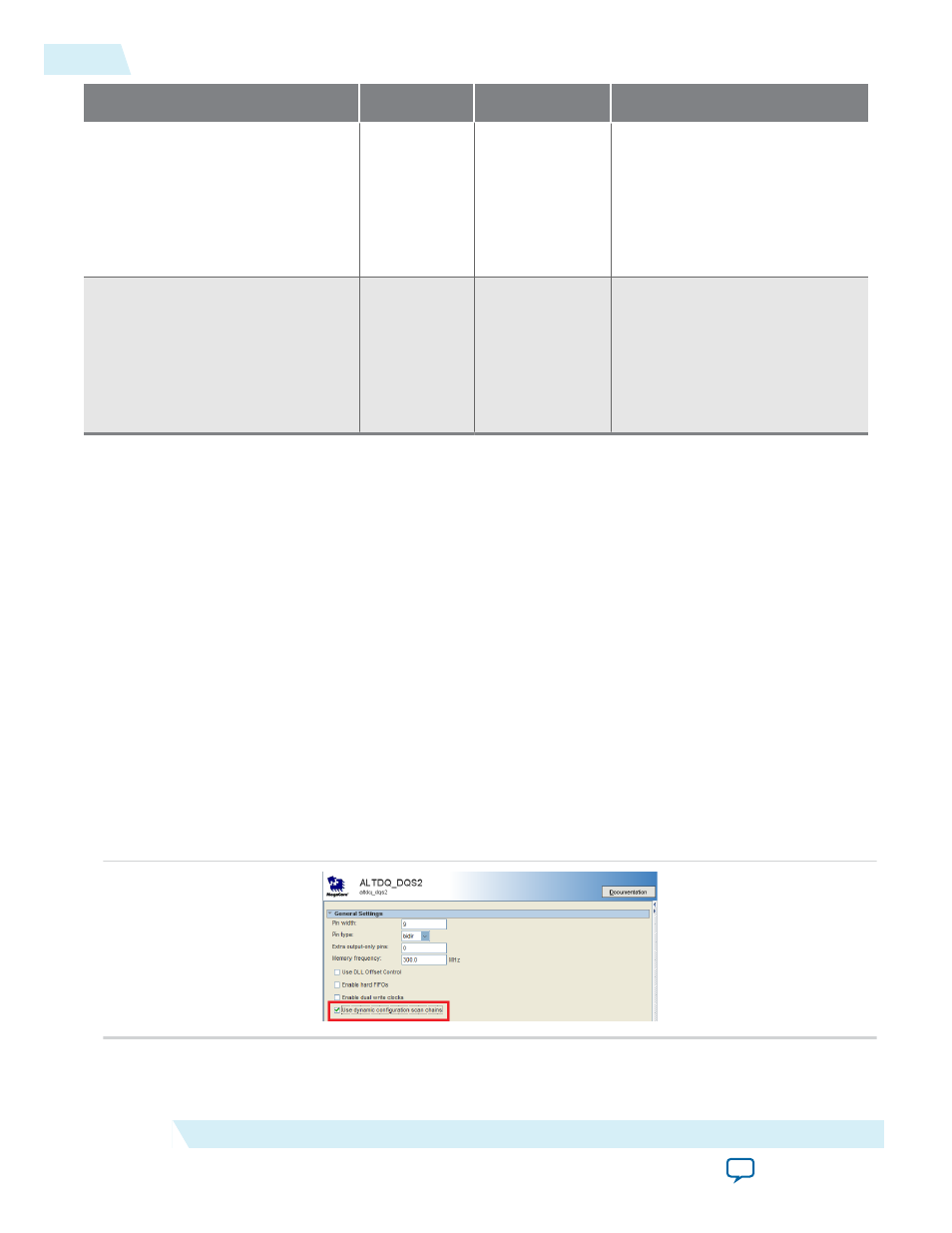

Dynamic Reconfiguration for ALTDQ_DQS2

When static timing closure is challenging (for example, high frequency, high board trace skew, and high

timing uncertainty), dynamically reconfiguring the ALTDQ_DQS2 IP core may provide additional timing

margin. Arria V, Cyclone V, and Stratix V devices contain reconfigurable logic, allowing you to adjust the

delay of several datapaths at runtime.

The I/O configuration block and the DQS configuration block are shift registers that you can use to

dynamically change the settings of various device configuration bits. The shift registers are configured

with the rest of the device when the Programmer Object File (.pof). In dynamic mode, you can override

the static values at runtime with a scan chain. You can reconfigure the I/Os by turning on the Use

dynamic configuration scan chains option.

The following figure shows the Use dynamic configuration scan chains option.

Figure 16: Use Dynamic Configuration Scan Chains Option

The following figure shows the dynamic reconfiguration scan chain implementation.

38

Dynamic Reconfiguration for ALTDQ_DQS2

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide