Altdq_dqs2 data strobe ports – Altera ALTDQ_DQS2 User Manual

Page 26

ALTDQ_DQS2 Data Strobe Ports

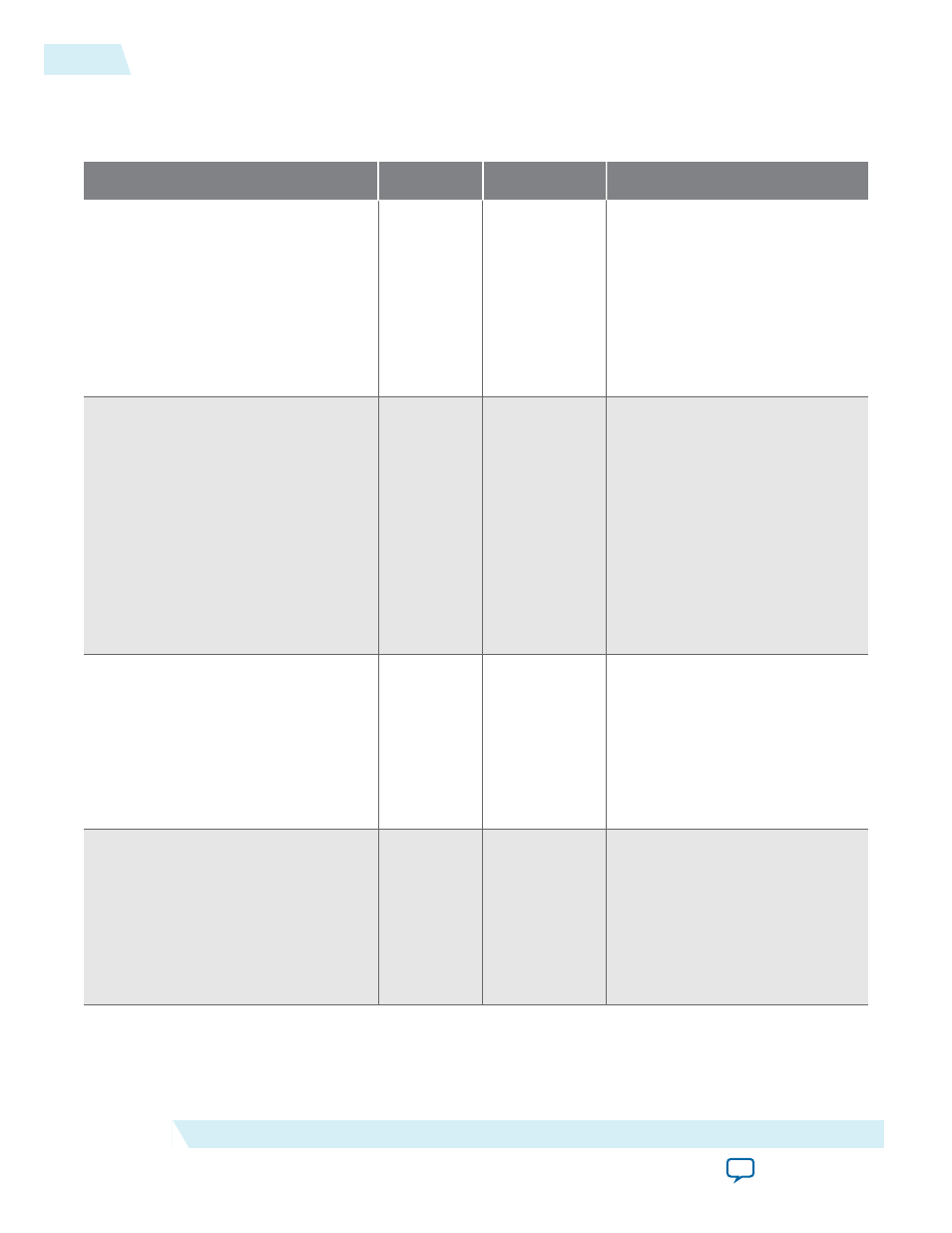

Table 6: ALTDQ_DQS2 Data Strobe Ports

Port Name

Type

Width

Description

capture_strobe_ena

Input

1

Controls the DQS enable control

block by acting as the gating

signal for signals coming from

the input registers (

capture_

strobe_in

) to reach the DQS

delay chain block.

This port is only supported in

Stratix V devices.

capture_strobe_n_in

Input

1

Receives the negative polarity

clock signal from the external

device. For example, a

DQSn

signal from the external

memory. This port is available

when the capture strobe type is

set to differential or complemen‐

tary.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

capture_strobe_in

Input

1

Receives the clock signal from

the external device, for example,

a DQS signal from the external

memory.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

capture_strobe_out

Output

1

Sends the delayed clock signal to

the core. For example, a delayed

DQS signal from the DQS delay

chain.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

26

ALTDQ_DQS2 Data Strobe Ports

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide