Altdq_dqs2 dynamic configuration ports – Altera ALTDQ_DQS2 User Manual

Page 35

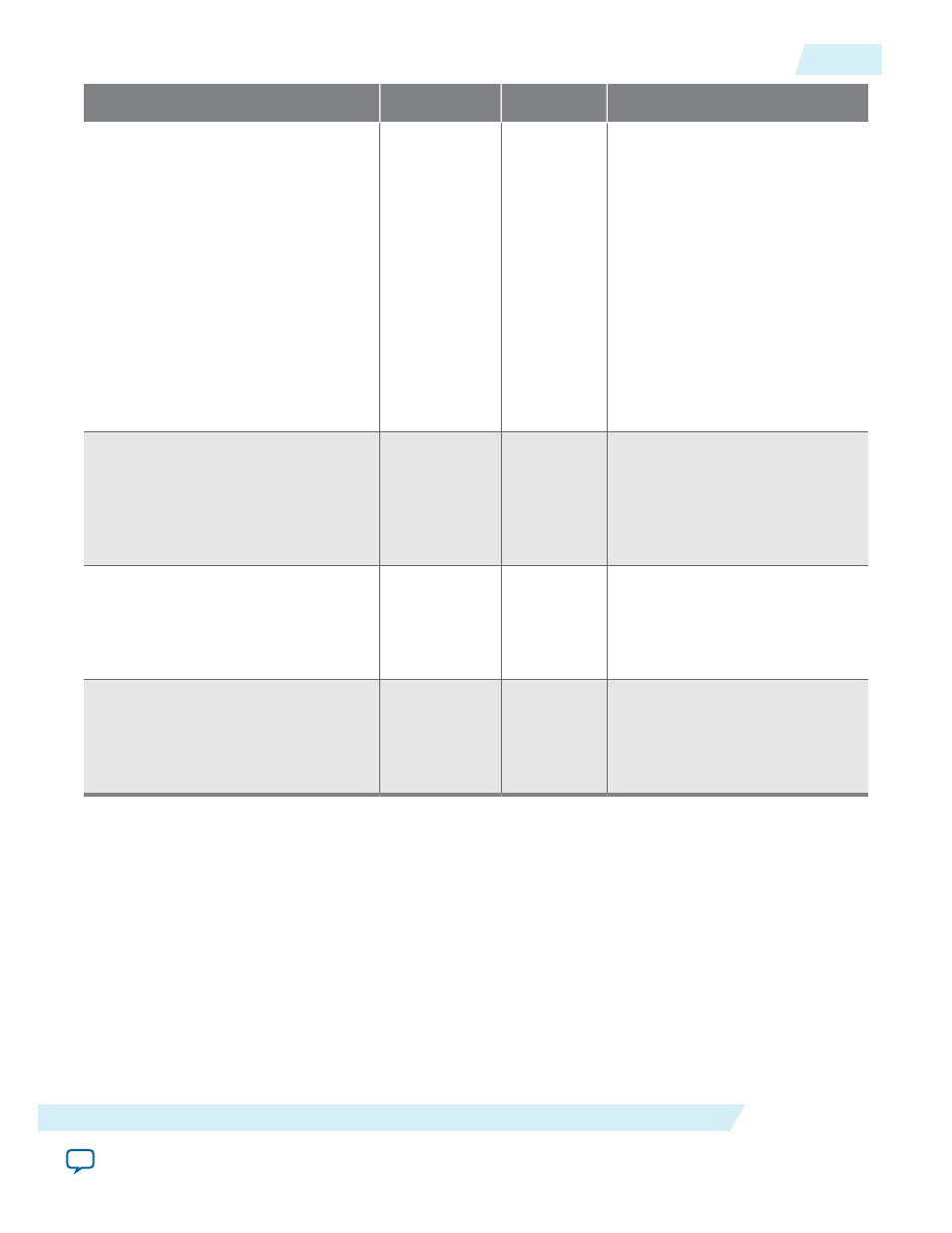

Ports

Type

Width

Description

vfifo_qvld

Input

Arria V and

Cyclone V

devices: 2

Stratix V

devices: 1

Data input to the data valid

FIFO. This signal is the full read

enable token generated by user

logic and is asserted for the

length of the desired read burst.

This signal is driven by the same

user logic that drives the

lfifo_

rdata_en_full

signal.

In general applications, you can

leave this port unconnected.

This port is supported in Arria

V, Cyclone V, and Stratix V

devices.

vfifo_inc_wr_ptr

Input

2

Increments the latency

implemented by the data valid

FIFO by one cycle.

This port is only supported in

Arria V and Cyclone V devices.

vfifo_reset_n

Input

1

Active high reset to the data

valid FIFO

This port is only supported in

Arria V and Cyclone V devices.

rfifo_reset_n

Input

1

Active high reset to the read

FIFO .

This port is only supported in

Arria V and Cyclone V devices.

The I/O and DQS configuration blocks represent a set of serial-to-parallel shift registers that dynamically

changes the settings of various device configuration bits. The I/O and DQS configuration blocks shift a

serial configuration data stream into the shift registers, and then load the data stream into the configura‐

tion registers. The shift registers power-up low. Every I/O pin contains an I/O configuration block. Every

DQS group contains a DQS configuration block and an I/O configuration block.

ALTDQ_DQS2 Dynamic Configuration Ports

The following table lists the dynamic configuration ports where n= number of DQ pins and m= number

of additional DQ pins.

UG-01089

2014.12.17

ALTDQ_DQS2 Dynamic Configuration Ports

35

ALTDQ_DQS2 IP Core User Guide

Altera Corporation