Timing violation – Altera ALTDQ_DQS2 User Manual

Page 95

The following

set_false_path

commands ensure that we are analyzing only the same edge

transfers, by removing the opposite edge transfers.

Note: These assignments are optional.

Example 11: set_false_path Commands

set_false_path -setup -rise_from [get_clocks{pll_inst|alterapll_inst|

altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}] -fall_to [get_clocks

{dqs_out}]

set_false_path -setup -fall_from [get_clocks{pll_inst|alterapll_inst|

altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}] -rise_to [get_clocks

{dqs_out}]

set_false_path -hold -rise_from [get_clocks{pll_inst|alterapll_inst|

altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}] -rise_to [get_clocks

{dqs_out}]

set_false_path -hold -fall_from [get_clocks{pll_inst|alterapll_inst|

altera_pll_i|general[3].gpll~PLL_OUTPUT_COUNTER|divclk}] -fall_to [get_clocks

{dqs_out}]

The strobe port functions as input or output at a time. Non-related transfers below should be set to false

path and do not need to be analyzed.

set_false_path -from [get_clocks {virtual_dqs_in}] -to [get_clocks {dqs_out}]

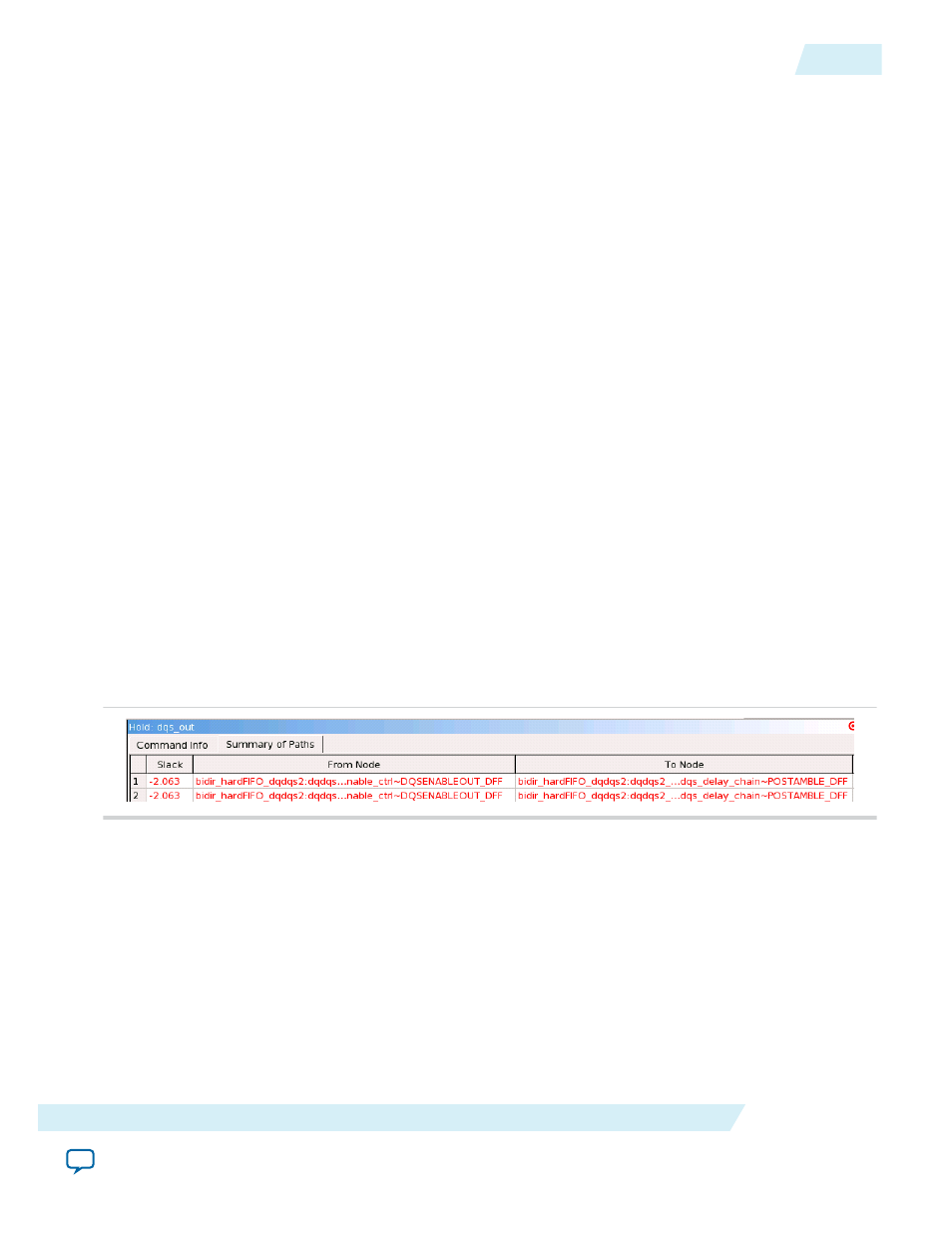

Timing Violation

The following figure shows a timing violation in the example design. This path is related to DQS enable

control and is valid. Some calibration algorithm is required to control the DQS enable block.

Figure 68: Timing Violation

Without any calibration algorithm in place, this path cannot be set as false path in the static timing

analysis.

Example 12: set_false_path Command

#set_false_path -from [get_keepers {*|dqs_enable_ctrl~DQSENABLEOUT_DFF}] -to

[get_clocks{dqs_out}]

Related Information

•

For more information related to the PHY Clock and DQS Logic Blocks.

UG-01089

2014.12.17

Timing Violation

95

ALTDQ_DQS2 IP Core User Guide

Altera Corporation