Altera ALTDQ_DQS2 User Manual

Page 12

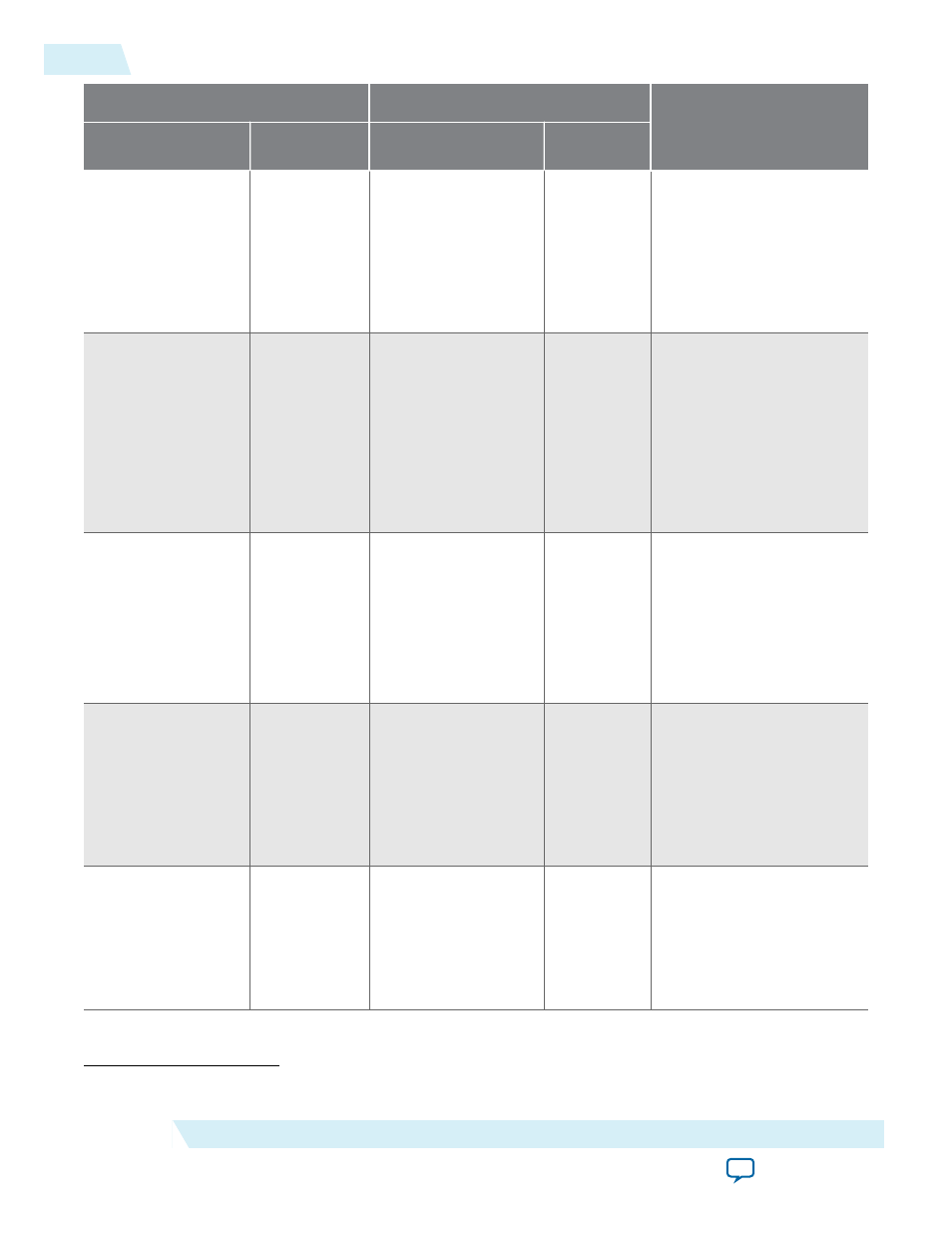

Parameter Editor GUI Setting

CLI Parameter

Description

Name

Legal Values

Name

Legal

Values

(1)

Memory frequency 1–1068

INPUT_FREQ

120–1068

This setting specifies the

full-rate clock frequency

of the incoming DQS

group signal from the

external device in MHz.

The default value is

300 MHz (

300

).

Use DLL Offset

Control

—

USE_OFFSET_CTRL

true

false

This setting enables

dynamic control of the

DLL offset.

Altera recommends using

this setting for test

purposes only. For DQS

data capture calibration,

use the D1, D2, D3, and

D4 delay chains.

Enable hard FIFOs —

USE_HARD_FIFOS

true

false

This setting enables the

hard FIFOs (read FIFO for

Stratix V devices and read

FIFO, latency shifter FIFO

and data valid FIFO for

Arria V and Cyclone V

devices) as part of the

ALTDQ_DQS2 IP core.

Use Capture Clock

to clock the read

Side of the Hard

VFIFO

—

USE_DQSIN_FOR_

VFIFO_READ

true

false

Turn on this setting when

you use the hard data valid

FIFO and when the

capture clock is not gated.

This setting is available

only for Arria V and

Cyclone V devices.

Enable dual write

clocks

—

DUAL_WRITE_CLOCK

true

false

This setting enables the

use of separate output

clocks for data and strobe.

This setting is disabled by

default for Arria V and

Cyclone V devices.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

12

ALTDQ_DQS2 Parameter Settings

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide