Altera ALTDQ_DQS2 User Manual

Page 39

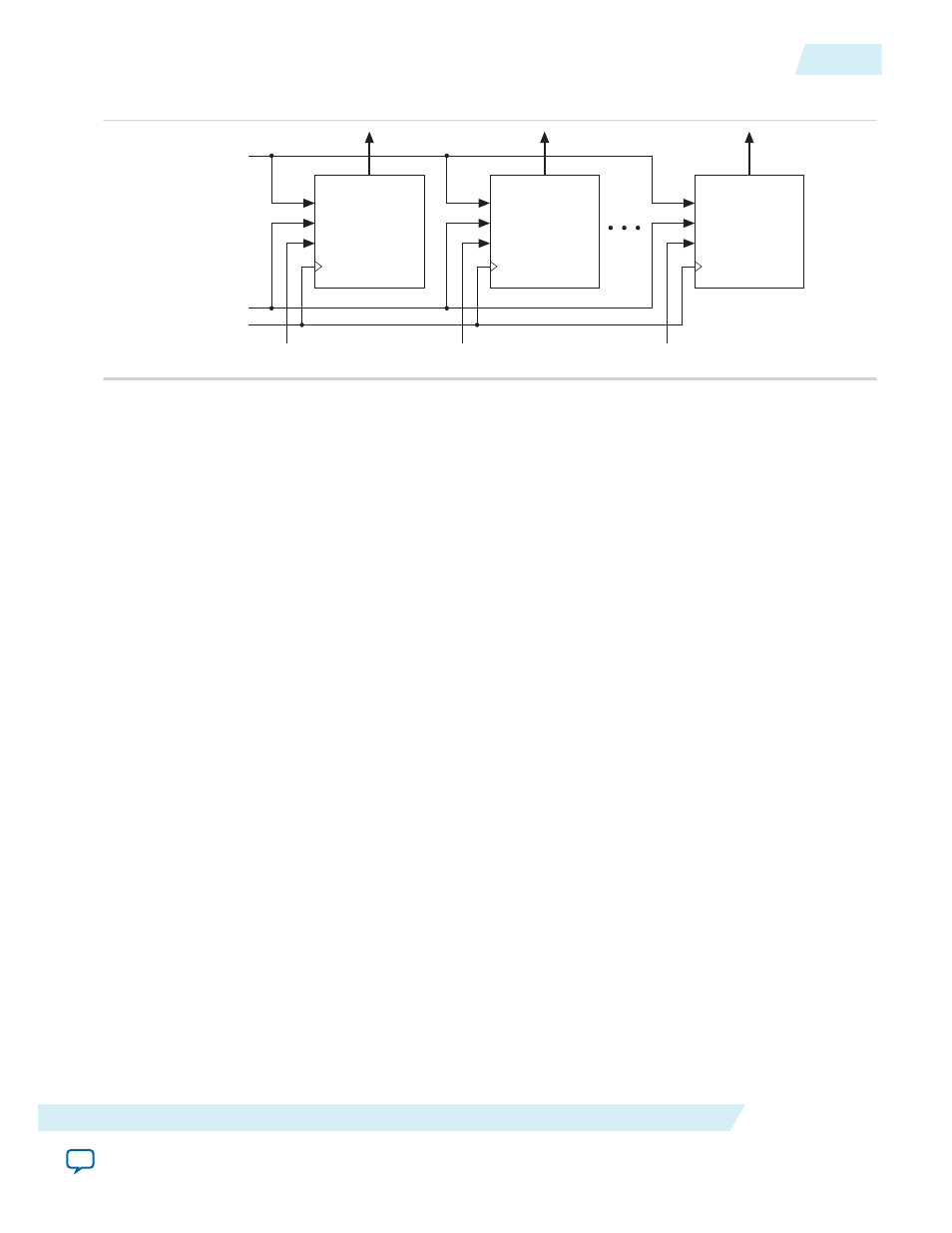

Figure 17: Reconfiguration Scan Chain

din

update

enable

clk

DQ0

din

update

enable

clk

DQ1

din

update

enable

clk

DQS

config_data

config_update

config_clock_in

config_io_ena[0]

config_io_ena[1]

config_dqs_ena

Each I/O contains a scan chain block. The DQS logic also contains its own scan chain block. You can use

I/O scan chain blocks to configure DQ and DQS I/O configuration registers (for example, delay chain)

and you can use the DQS logic scan chain to configure DQS logic configuration (for example, DQS

postamble phase). You can serially scan configuration bits into each scan chain block with the following

operating sequence:

The ALTDQ_DQS2 dynamic configuration interface is made of four input ports:

•

config_clock_in

—This is the clock signal. All other input signals must be treated as synchronous to

this clock. The typical frequency is 25 MHz.

•

config_data

—This is the 1-bit serial input through which data is scanned into the calibration blocks.

This is common to all configuration blocks, but it will only be scanned into calibrations blocks whose

enable input is asserted. Configuration data must be input in LSB first ordering. For example, the

Stratix V I/O configuration block data must start with

padtoinputregisterdelaysetting[0]

.

•

config_enable

—In a generic ALTDQ_DQS2 IP core, the following three

config_enable

inputs are

available:

•

config_io_ena[]

—Controls the enable input on the DQ I/Os

•

config_dqs_io_ena[]

—Controls the enable input on the DQS I/Os

•

config_dqs_ena[]

—Controls the enable input on the DQS logic

Note: Each of these inputs is wide to control all the scan chain blocks instantiated in the

ALTDQ_DQS2 IP core. In a general application, you must assert only one enable input at a

time to scan the desired data in the corresponding scan chain block. The enable input must be

held high for the entire duration of the scanning process. All other inputs must be held at 0.

Note: You must deassert the

config_enable

signal after the last bit of

config_data

to prevent

further data from scanning in. Then, assert the

update

signal whenever you are ready to copy

the scanned in data to the configuration registers.

•

config_update

—After scanning all the bits into the desired scan chain blocks, copy them into the

configuration register by asserting the

config_update

signal for one clock cycle.

UG-01089

2014.12.17

Dynamic Reconfiguration for ALTDQ_DQS2

39

ALTDQ_DQS2 IP Core User Guide

Altera Corporation