Altdq_dqs2 hard fifo ports – Altera ALTDQ_DQS2 User Manual

Page 34

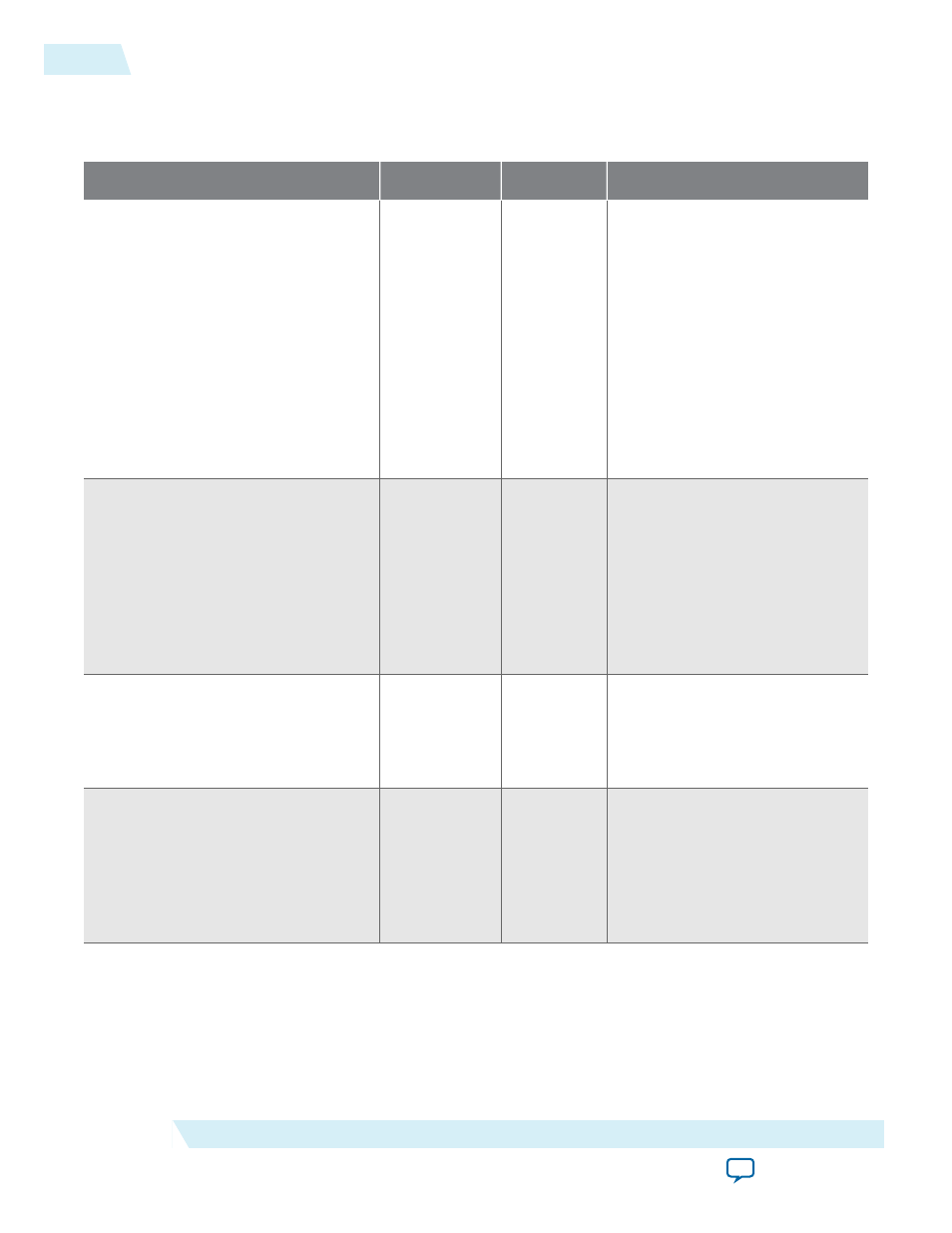

ALTDQ_DQS2 Hard FIFO Ports

Table 10: Hard FIFO Ports

Ports

Type

Width

Description

lfifo_rdata_en_full

Input

2

Data input to the latency shifter

FIFO. This signal is the full read

enable token generated by user

logic and is asserted for the

length of the desired read burst.

This token is delayed by a

variable number of integer cycles

inside the latency shifter FIFO

and used to feed the read enable

signal of the read FIFO.

This port is only supported in

Arria V and Cyclone V devices.

lfifo_rden

Input

1

Data input to the Read FIFO

Read Enable. This signal is the

full read enable token generated

by user logic and is asserted for

the length of the desired read

burst.

This port is only supported in

Stratix V devices.

lfifo_reset_n

Input

1

Active high reset to the latency

shifter FIFO

This port is only supported in

Arria V and Cyclone V devices.

lfifo_rd_latency[]

Input

5

The number of cycles to delay

data inputs feeding the latency

shifter FIFO. A maximum of 31

cycles is supported.

This port is only supported in

Arria V and Cyclone V devices.

34

ALTDQ_DQS2 Hard FIFO Ports

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide