Altera ALTDQ_DQS2 User Manual

Page 41

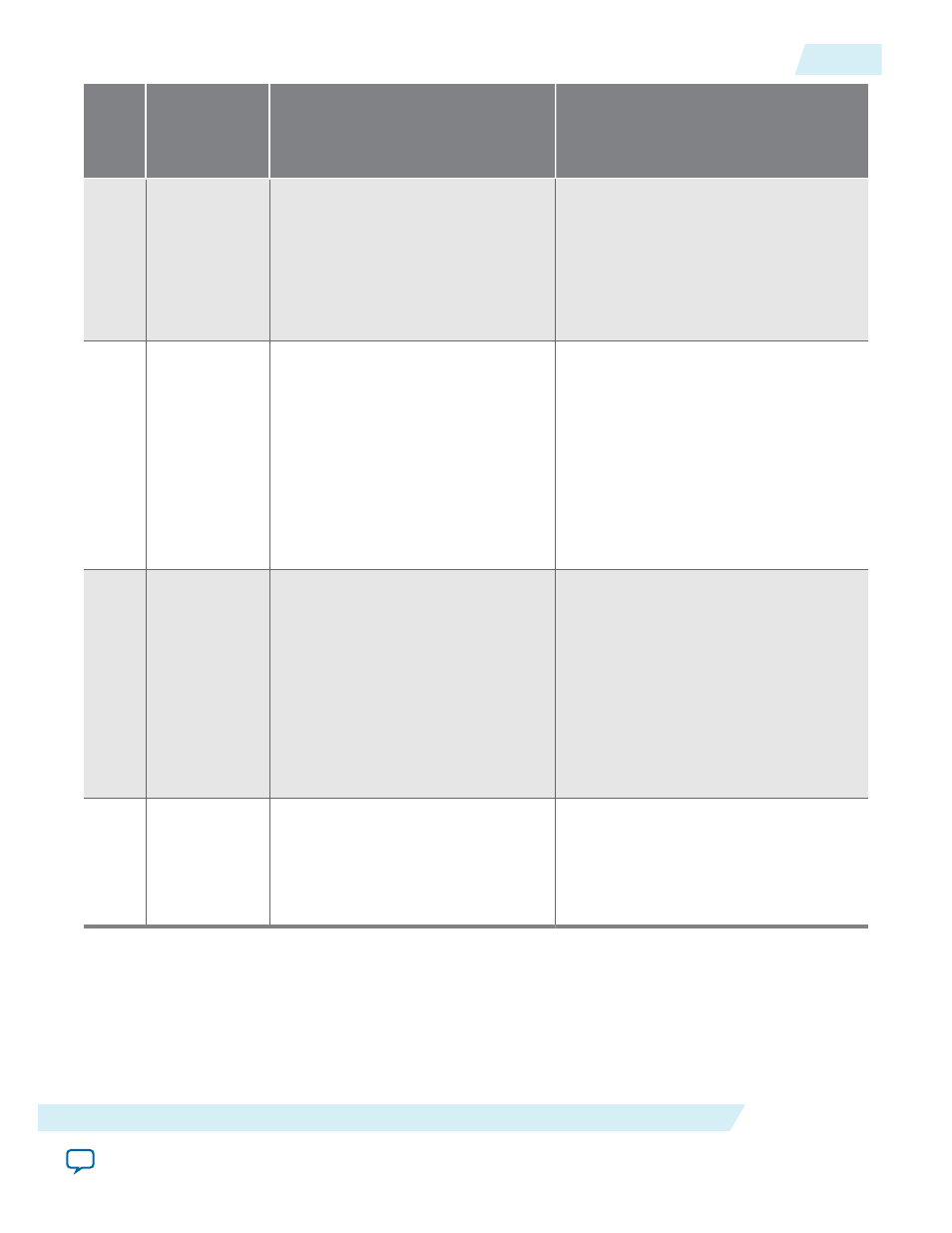

Legend

in

Bit

Bit Name

Description

B

11..6

padtoinputregisterrisefalldelaysetting

Connects to the

delayctrlin

port of

the second D1 delay chain to control the

second pad-to-input register delay chain

(D1).

For delay values, refer to the “Program‐

.

C

17..12

outputdelaysetting1

Connects to the

delayctrlin

port of

the D5 delay chain to control the output

register-to-I/O buffer delay chain (D5)

in the output path and output enable

paths.

This delay is for write calibration for

DDR application.

For delay values, refer to the “Program‐

.

D

23..18

outputdelaysetting2

Connects to the

delayctrlin

port of

the second D5 delay chain to control the

output register-to-I/O buffer delay chain

(second D5) in the output path and

output enable paths.

This delay is for write calibration for

DDR application.

For delay values, refer to the “Program‐

.

— 39..24

inputclkndelaysetting

inputclkdelaysetting

dutycycledelaymode

dutycycledelaysetting

Unconfigurable bits.

Always set bits to its default value.

UG-01089

2014.12.17

I/O Configuration Block Bit Sequence for Arria V GZ and Stratix V Devices

41

ALTDQ_DQS2 IP Core User Guide

Altera Corporation