Altera ALTDQ_DQS2 User Manual

Page 58

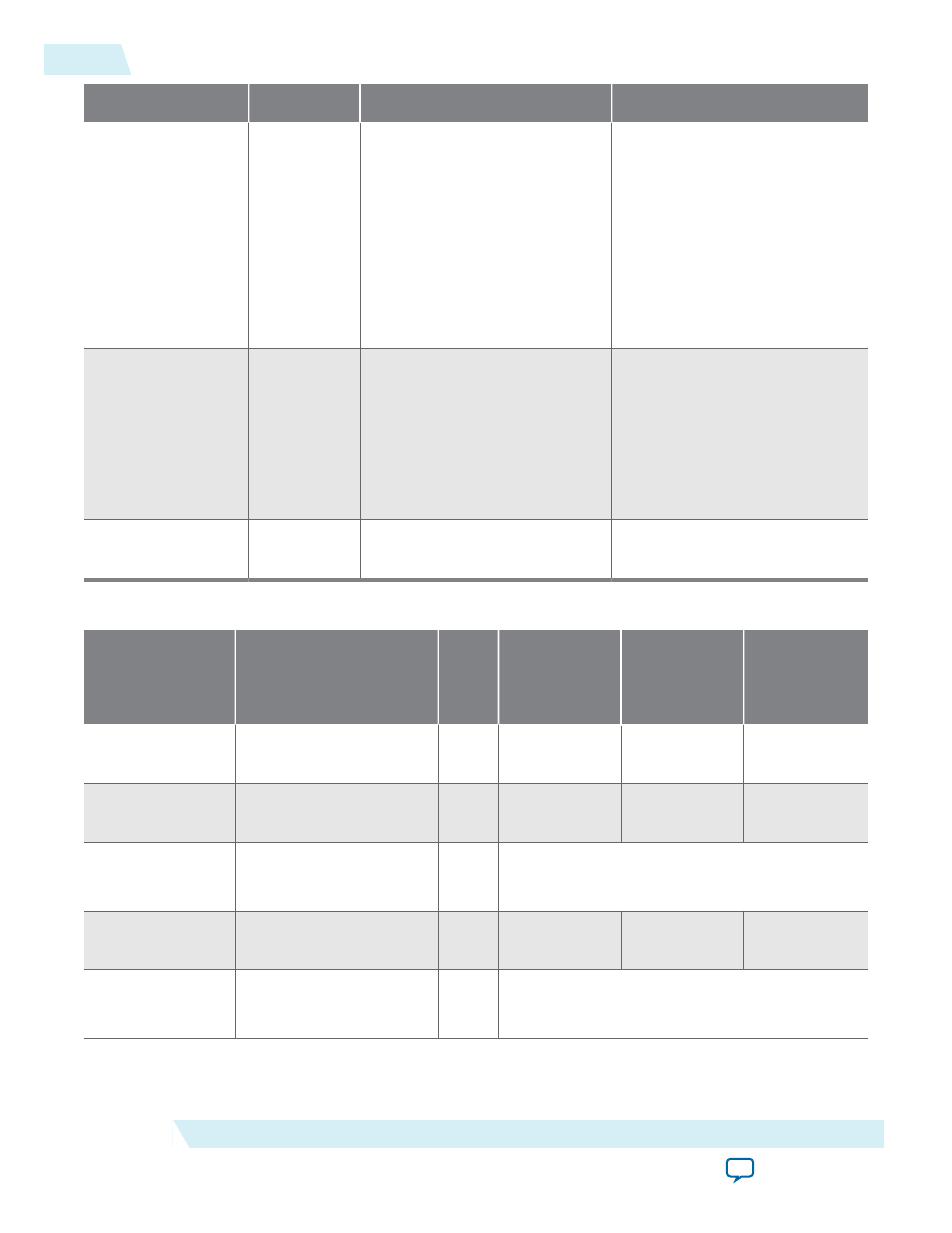

Legend in

Bit

Bit Name

Description

M

22

postamblephaseinvert

Connects to the phaseinvertctrl

port of the clock phase select

block to select between the non-

inverted and inverted output.

This clock phase select block is

used to level the postamble

clock (in leveling multiplexer).

This setting allows the phase

output from the delay chain to

be inverted to gain additional

phases.

N

24..23

postamblephasesetting

Connects to the phasectrlin port

of the clock phase select block to

select between phase shifts of 0°,

45°, 90°, and 135°. This

particular clock phase select

block is used to level the

postamble clock (in leveling

multiplexer).

—

29..25

Not mapped to any port

Unconfigurable bits. Always set

bits to its default value.

Table 19: DQS Configuration Block Bit Value for Arria V and Cyclone V Devices

Bit

External Bit Name

Defaul

t Value

(Binary

)

Min. Value

Max. Value

Inc. Value

4..0

dqsenableungatingdelayset‐

ting

0

intrinsic delay

775 ps +

intrinsic delay

25 ps

9..5

dqsenablegatingdelaysetting

0

intrinsic delay

775 ps +

intrinsic delay

25 ps

10

enadqsenablephasetrans‐

ferreg

0

0: Disable Neg-Edge Register

1: Enable Neg-Edge Register

15..11

octdelaysetting

0

intrinsic delay

775 ps +

intrinsic delay

25 ps

16

dqshalfratebypass

0

0: Engage Half-Rate Register

1: Bypass Half-Rate Register

58

DQS Configuration Block Bit Sequence for Arria V and Cyclone V Devices

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide