Altera ALTDQ_DQS2 User Manual

Page 13

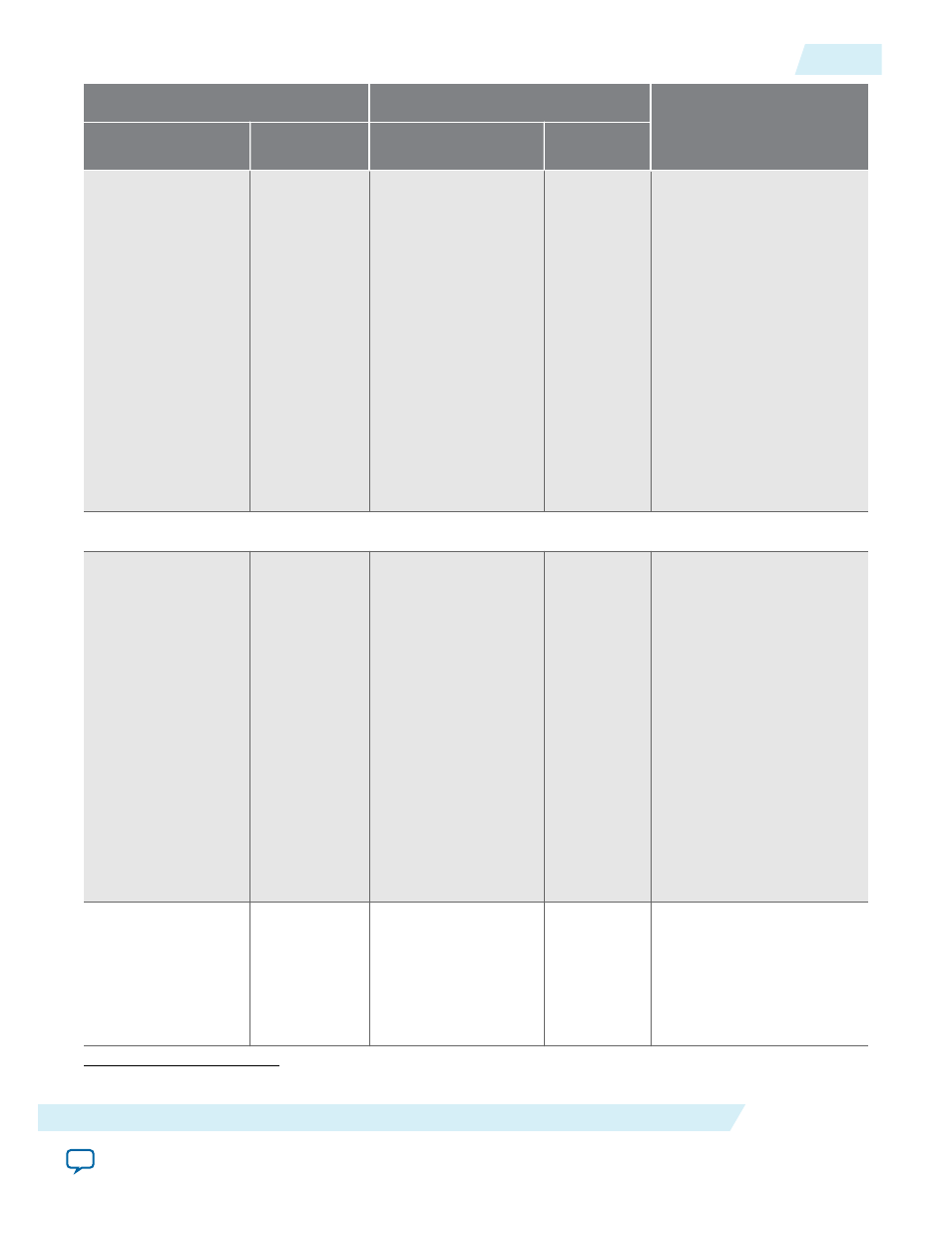

Parameter Editor GUI Setting

CLI Parameter

Description

Name

Legal Values

Name

Legal

Values

(1)

Use dynamic

configuration scan

chains

—

USE_DYNAMIC_CONFIG

true

false

This setting enables

run-time configuration of

multiple delay chains,

phase shifts, and transfer

registers.

Requires a correctly

formatted bitstream.

For more information,

on page

Output Path

Use half-rate

output path

—

HALF_RATE_OUTPUT

true

false

This setting doubles the

width of the data bus on

the FPGA side and clocks

the FPGA side interface

using the half-rate clock

input.

If this setting is enabled,

drive the

hr_clock_in

port with the half-rate

clock signal.

When enabling hard read

FIFO in a Stratix V device,

you must set this

parameter to

true

.

This setting is enabled by

default.

Use output phase

alignment blocks

—

USE_OUTPUT_PHASE_

ALIGNMENT

true

false

This setting enables phase

shift on the output path

based on the delay settings

from the DLL.

This setting is disabled by

default.

(1)

All CLI parameter values are type string, therefore you must enclose the values in double quotes.

UG-01089

2014.12.17

ALTDQ_DQS2 Parameter Settings

13

ALTDQ_DQS2 IP Core User Guide

Altera Corporation