Fifo control – Altera ALTDQ_DQS2 User Manual

Page 21

pointers. For protocols using a bidirectional strobe, the write enable signal is tied to VCC and DQS

gating/ungating implements the write enable functionality.

For Arria V and Cyclone V devices, the hard data valid FIFO internally generates the write enable (or

gating/ungating) signal, while the hard latency FIFO internally generates the read enable signal.

FIFO Control

For Arria V and Cyclone V devices, in addition to the read FIFO and the data valid FIFO, the location of

the latency shifter FIFO is in each DQS group. The latency shifter FIFO takes in a read-enable command

from the core and implements a programmable latency of up to 32 cycles before feeding into the read-

enable port of the read FIFO.

You can use the output of the data valid FIFO to perform the following tasks:

• To ungate the DQS logic when a strobe signal is capturing the data. In this case, the write-enable port

must always be '1' on the read FIFO.

• To enable the read FIFO write-enable port when a clock is in use.

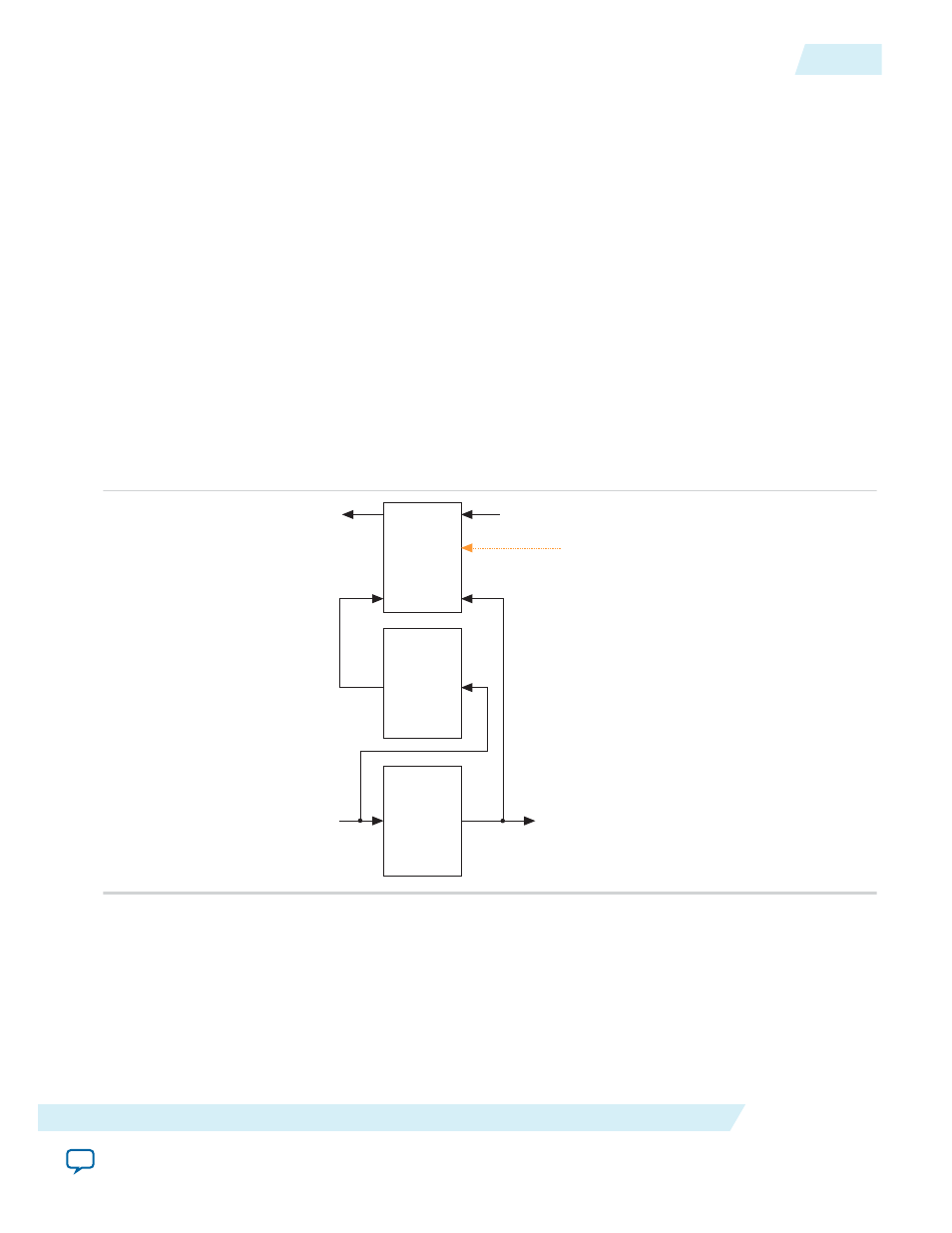

The following figure shows the three FIFOs interconnection.

Figure 11: Data Valid FIFO, Latency Shifter FIFO, and Read FIFO Interconnection

The read FIFO block is a hard FIFO in Arria V,

Cyclone V, and Stratix V devices. The latency

shifter FIFO and data valid FIFO are hard

FIFO in Arria V and Cyclone V devices.

Read

FIFO

DOUT

DIN

REN

WREN

Latency

Shifter

FIFO

Data

Valid

FIFO

Data to Core

Data from DQ

To DQS Enable

Read Data Enable from Core

When a read command is sent to the memory device, a read-data-enable token is pushed through the data

valid FIFO and the latency shifter FIFO. The data valid FIFO implements a latency equal to the read

command to data latency. When the token comes out of the data valid FIFO, the DQS signal is ungated.

The latency shifter FIFO then creates enough space between write and read pointers in the read FIFO to

ensure that the data read on the read side is correct. If the read FIFO is read at half-rate, the read FIFO

also implements a full-rate to half-rate conversion.

UG-01089

2014.12.17

FIFO Control

21

ALTDQ_DQS2 IP Core User Guide

Altera Corporation