Altera ALTDQ_DQS2 User Manual

Page 25

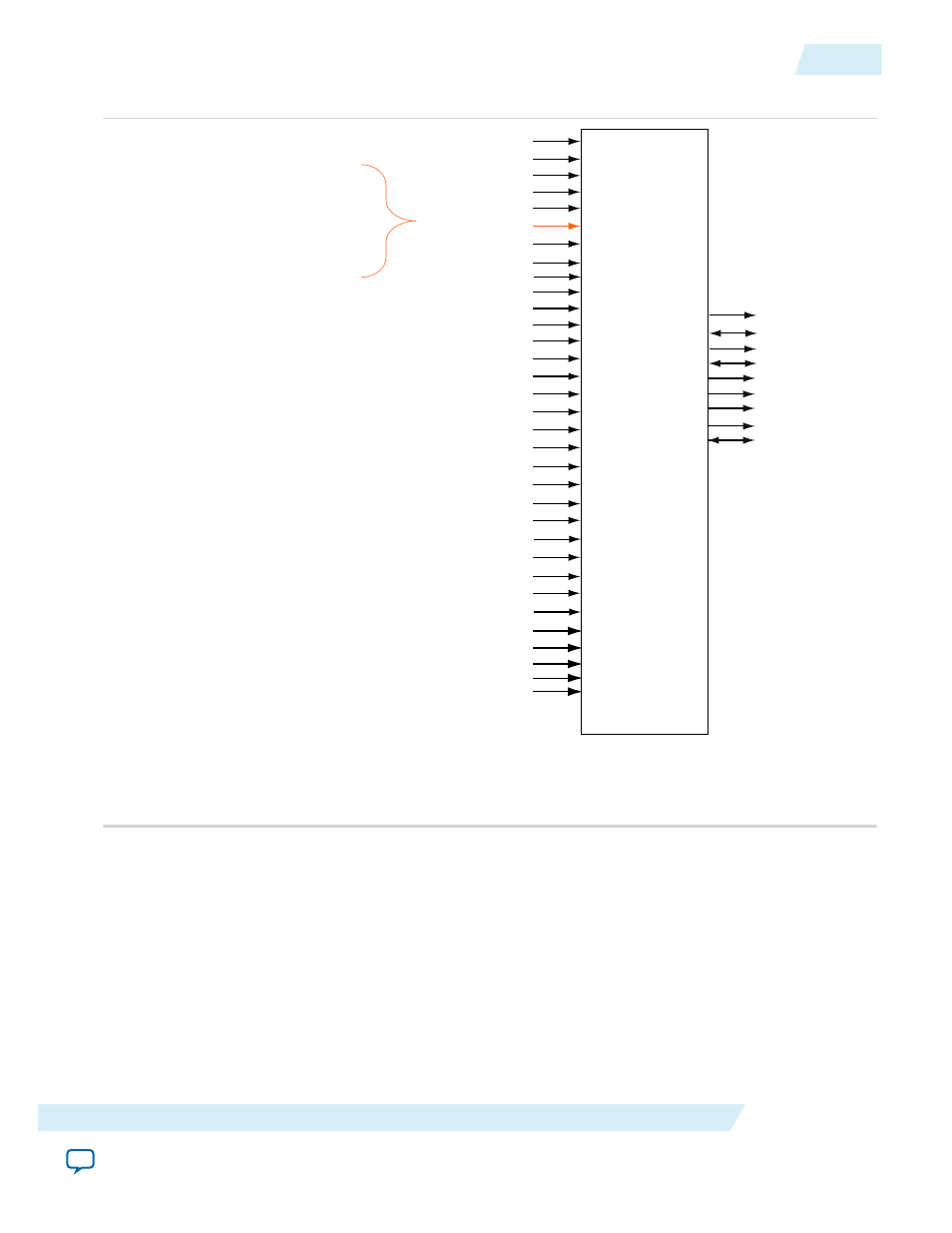

Figure 15: ALTDQ_DQS2 Block Diagram by Port Types

-

ALTDQ_DQS2

config_clock_in

config_data_in

config_dqs_ena

config_dqs_io_ena

config_update

core_clock_in

fr_clock_in

hr_clock_in

lfifo_rden

reset_n_core_clock_in

rfifo_reset_n

strobe_ena_hr_clock_in

vfifo_reset_n

write_strobe_clock_in

dll_delayctrl_in[]

capture_strobe_ena[]

output_strobe_ena[]

oct_ena_in[]

parallelterminationcontrol_in[]

seriesterminationcontrol_in[]

write_oe_in[]

output_strobe_n_out

output_strobe_out

extra_write_data_out[]

write_data_out[]

strobe_n_io

capture_strobe_out

read_data_out[]

strobe_io

read_write_data_io[]

write_data_in[]

config_io_ena[]

lfifo_rdata_en_full[]

lfifo_rd_latency[]

vfifo_qvld[]

vfifo_inc_wr_ptr[]

capture_strobe_n_in

extra_write_data_in[]

read_data_in[]

config_extra_io_ena[]

lfifo_reset_n

capture_strobe_in

This signal is used for QDRII. This clock, unlike

other clocks, can be held at zero during initialization,

which is a requirement for QDRII. Use the core

clock signal for internal purposes. In a half-rate

application, the core clock signal is unconnected. In

a full-rate application, you must connect the core

clock signal to the full-rate clock.

UG-01089

2014.12.17

ALTDQ_DQS2 Ports

25

ALTDQ_DQS2 IP Core User Guide

Altera Corporation