Analyzing same edge transfer – Altera ALTDQ_DQS2 User Manual

Page 93

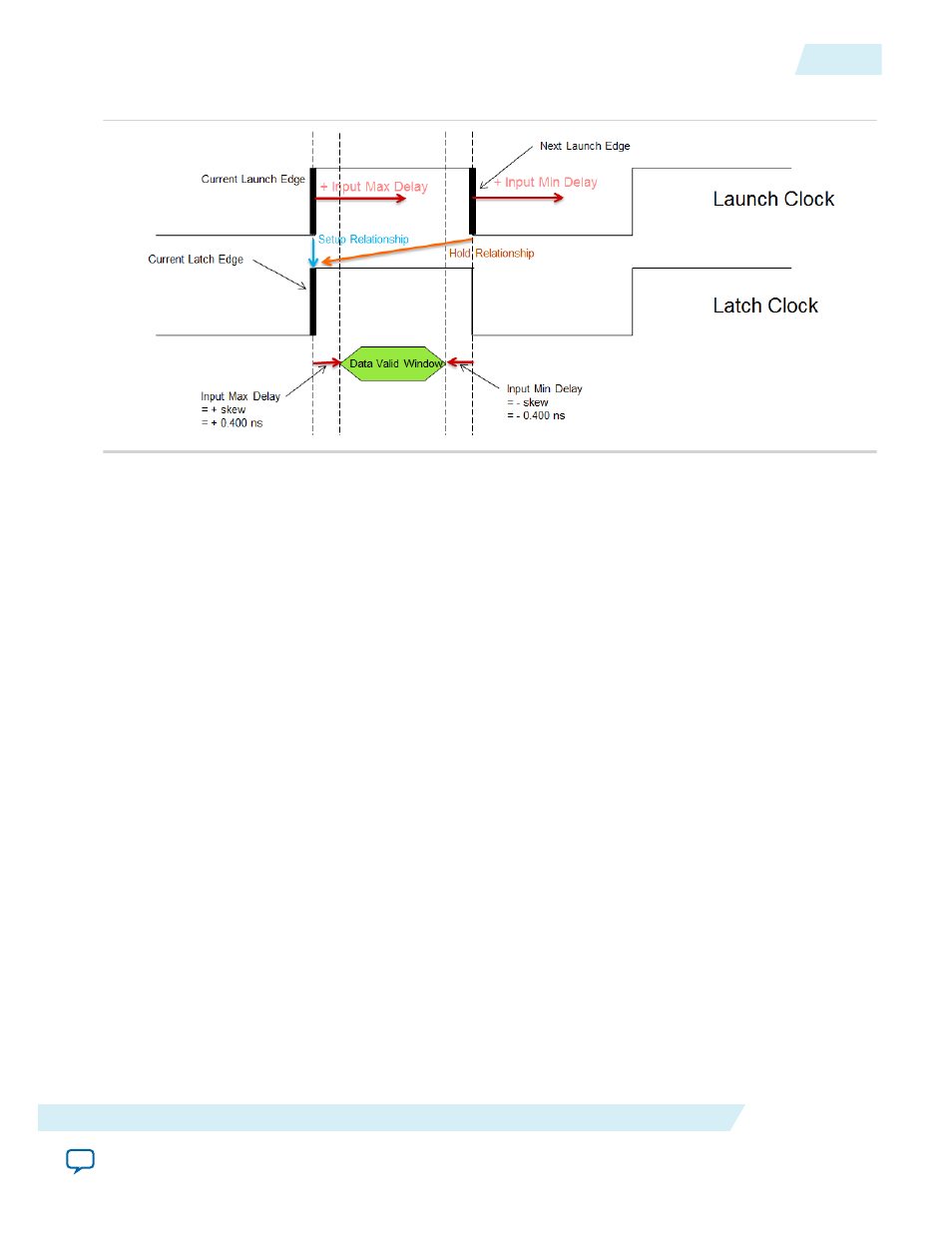

Figure 66:

Analyzing Same Edge Transfer

The following

set_false_path

commands ensure that you are analyzing only the same edge transfers, by

removing the opposite edge transfers.

Note: These assignments are optional.

Example 8: set_false_path Commands

set_false_path -setup -rise_from [get_clocks {virtual_dqs_in}] -fall_to

[get_clocks {dqs_in}]

set_false_path -setup -fall_from [get_clocks {virtual_dqs_in}] -rise_to

[get_clocks {dqs_in}]

set_false_path -hold -rise_from [get_clocks {virtual_dqs_in}] -rise_to

[get_clocks {dqs_in}]

set_false_path -hold -fall_from [get_clocks {virtual_dqs_in}] -fall_to

[get_clocks {dqs_in}]

The default setup relationship is to latch data on the next edge. The following

set_multicycle_path

commands direct the TimeQuest Timing Analyzer to analyze the paths as

a same-edge transfer, whereby the same edge that launches data is going to latch it. The reason it

is latched on the same edge is that latch edge will be delayed by the DQS circuitry (hardened 90°

in this design example) into the middle of the data eye.

Example 9: set_multicycle_path Commands

set_multicycle_path -rise_from [get_clocks {virtual_dqs_in}] -rise_to

[get_clocks {dqs_in}] -setup -end 0

set_multicycle_path -fall_from [get_clocks {virtual_dqs_in}] -fall_to

[get_clocks {dqs_in}] -setup -end 0

UG-01089

2014.12.17

Analyzing Same Edge Transfer

93

ALTDQ_DQS2 IP Core User Guide

Altera Corporation