Instantiating altdq_dqs2 ip core – Altera ALTDQ_DQS2 User Manual

Page 60

Instantiating ALTDQ_DQS2 IP Core

To instantiate the ALTDQ_DQS2 IP core, perform the following steps:

1. In the Quartus II software, open the Top_SV_13.0sp1.qar and restore the archived file into your

working directory.

2. In the IP Catalog (Tools > IP Catalog), locate and double-click the name of the IP core to customize.

The parameter editor appears.

3. Specify a top-level name for your custom IP variation. This name identifies the IP core variation files

in your project. If prompted, also specify the target Altera device family and output file HDL

preference. Click OK.

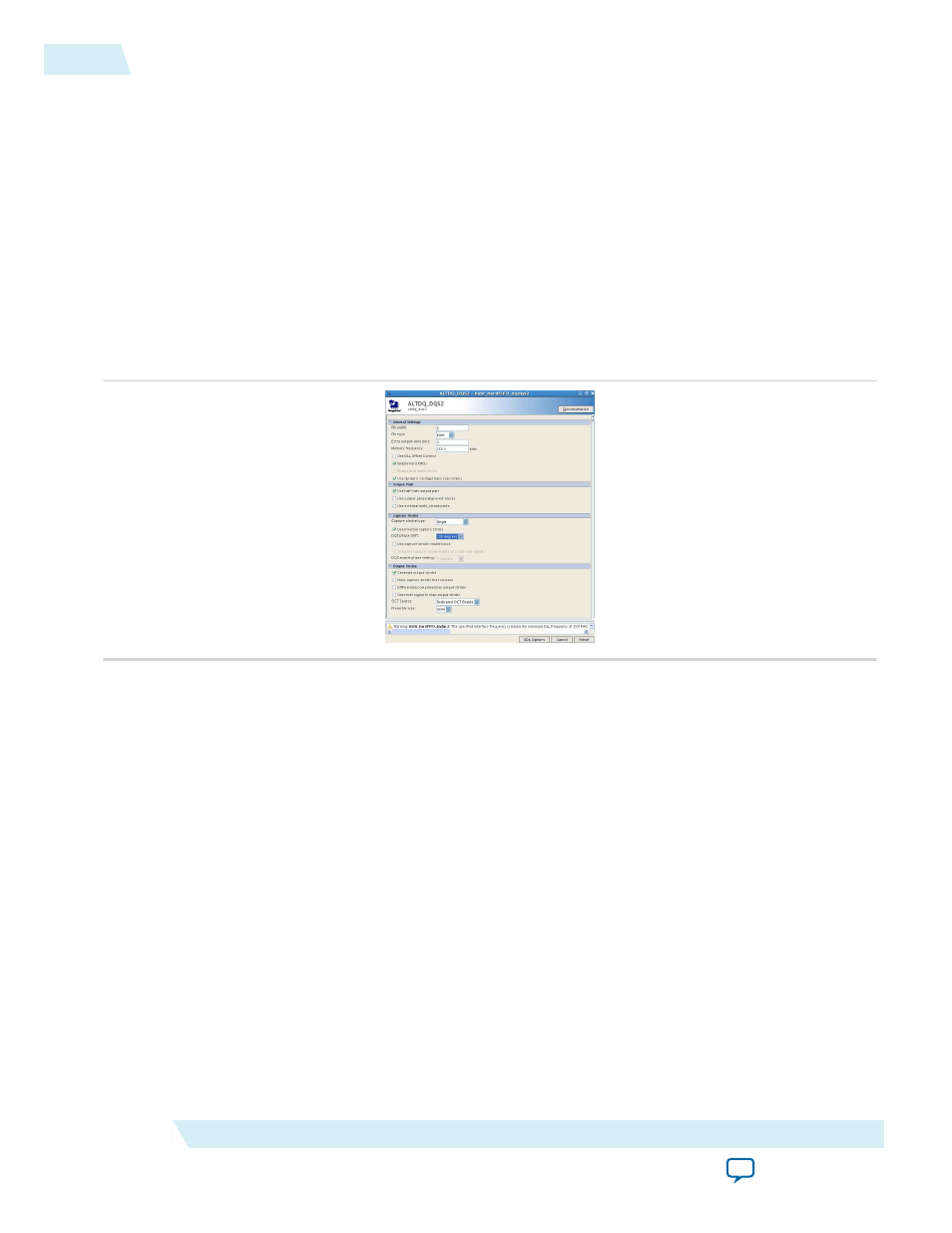

4. On the Parameter Settings tab, on the General page, specify the parameters as shown in the following

figure. These parameters configure the general settings for the ALTDQD_DQS2 instance.

Figure 21: ALTDQ_DQS2 Parameter Settings for Stratix V Devices

5. Click Finish.

Because the memory frequency is less than the DLL minimum frequency, the DLL needs to be driven

by a 2 x frequency (2 x 250 MHz = 500 MHz).

Because the DLL is driven at doubled frequency, the effective DQS delay is only half of the memory

frequency. In this case, to achieve 90 degree shift for memory frequency, the closest setting is 135

degree in the ALTDQ_DQS2 GUI (which is effectively only 135 degree of 500 MHz, or 67.5 degree of

250 MHz).

Note: The settings in

enables free-running read and write clock. DQS enable block is not

needed.

Note: If your design requires bidirectional strobe, turn on the Make capture strobe bidirectional

option. The timing of the capture strobe enables the DQS enable block to know the arrival of

the capture strobe which requires round-trip delay information. However, the use of the DQS

enable block requires runtime calibration which is not a feature of the ALTDQ_DQS2 IP core.

60

Instantiating ALTDQ_DQS2 IP Core

UG-01089

2014.12.17

Altera Corporation

ALTDQ_DQS2 IP Core User Guide