Comparison to the 8051, Comparison to the 8051 -16, Table 5-1. instruction timing comparison -16 – Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

Page 63: Table 5-1. instruction timing comparison

5-16

Ultra-High-Speed Flash

Microcontroller User’s Guide

Comparison to the 8051

The original 8051 needed 12 clocks per machine cycle and most instructions executed in either one or two machine cycles. Thus,

except for the MUL and DIV instructions, the 8051 used either 12 or 24 clocks for each instruction. Furthermore, each machine cycle

in the 8051 used two memory fetches. In many cases the second fetch was a dummy, and the extra clock cycles were wasted.

The ultra-high-speed microcontroller uses one clock per memory (or machine) cycle. Where there were primarily one- and two-cycle

instructions before, an instruction on the ultra-high-speed microcontroller may take between one and ten cycles. The divide instruction,

for example, requires 10 cycles. Note however, that the 10 cycles needed for the DIV AB instruction can be executed at one clock per

cycle (10 x 1 = 10 total clock cycles). The instruction is executed 4.8 times faster than the original 8051 architecture which required

four cycles at a rate of 12 clocks per cycle (4 x 12 = 48 total clock cycles). Each instruction is at least four times faster, with the high-

est throughput improvement being 24 times that of the original 8051 architecture.

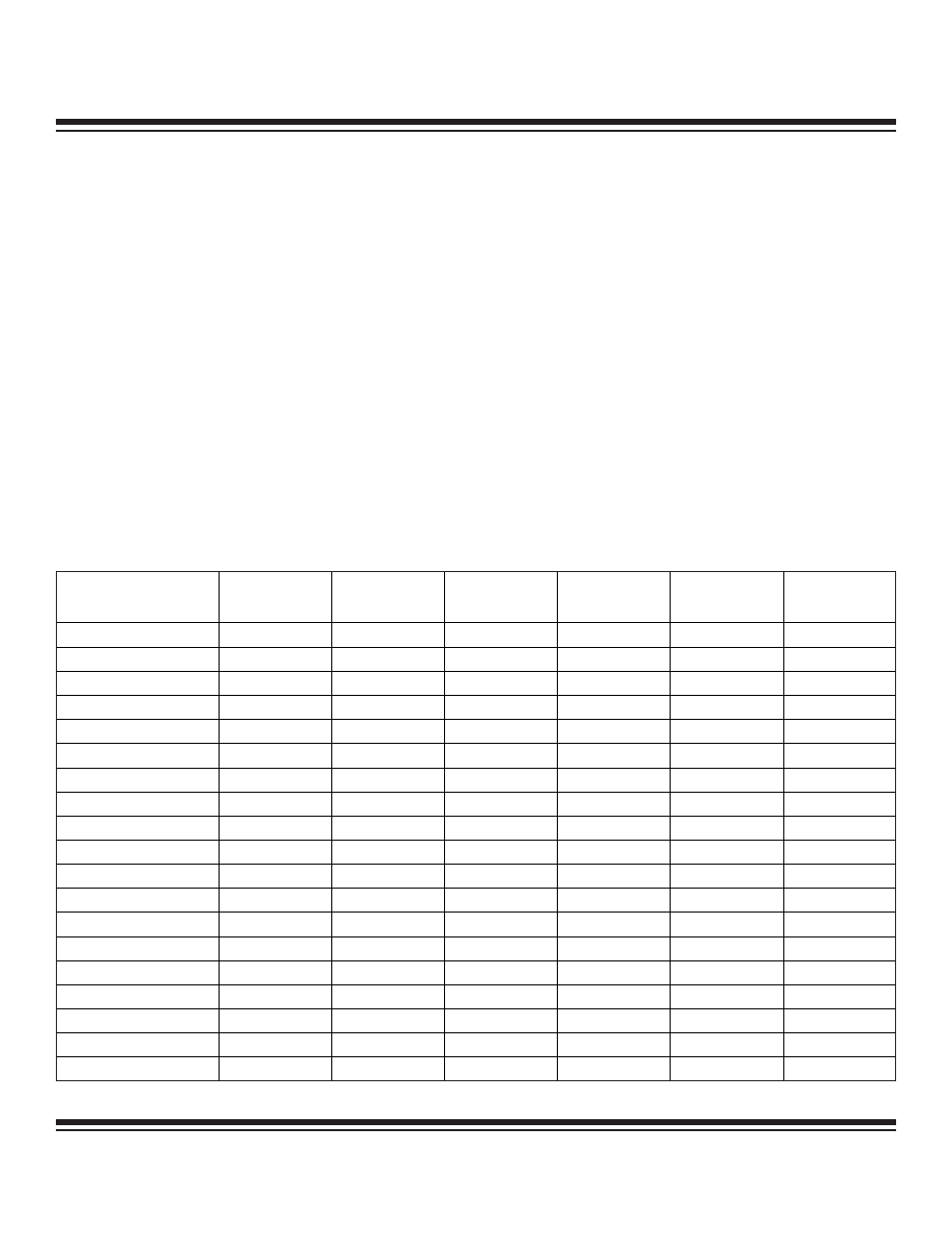

Table 5-1 shows each instruction, the number of clocks used in the ultra-high-speed microcontroller, and the number used in the 8051 for

comparison. The factor by which the ultra-high-speed microcontroller improves on the 8051 is shown as the speed advantage. A speed

advantage of 12 means that the ultra-high-speed microcontroller performs the same instruction 12 times faster than the original 8051.

Table 5-2 provides a summary by instruction type. Note that many of the instructions provide multiple op codes. As an example, the

ADD A, Rn instruction can act on one of eight working registers. There are eight op codes for this instruction because it can be used

on eight independent locations. Table 5-2 shows totals for both number of instructions and number of op codes. Averages are provid-

ed in the tables. However, the real speed improvement seen in any system depends on the instruction mix.

Table 5-1. Instruction Timing Comparison

Ultra-high-speed microcontroller is abbreviated as UHSM.

INSTRUCTION

HEX CODE

UHSM CLOCK

CYCLES

UHSM TIME @

25MHz

8051 CLOCK

CYCLES

8051 TIME @

25MHz

UHSM vs. 8051

SPEED

ADVANTAGE

ADD A, Rn

28..2F

1

40 ns

12

480 ns

12

ADD A, direct

25

2

80 ns

12

480 ns

6

ADD A, @Ri

26..27

2

80 ns

12

480 ns

6

ADD A, #data

24

2

80 ns

12

480 ns

6

ADDC A, Rn

38..3F

1

40 ns

12

480 ns

12

ADDC A, direct

35

2

80 ns

12

480 ns

6

ADDC A, @Ri

36..37

2

80 ns

12

480 ns

6

ADDC A, #data

34

2

80 ns

12

480 ns

6

SUBB A, Rn

98..9F

1

40 ns

12

480 ns

12

SUBB A, direct

95

2

80 ns

12

480 ns

6

SUBB A, @Ri

96..97

2

80 ns

12

480 ns

6

SUBB A, #data

94

2

80 ns

12

480 ns

6

INC A

04

1

40 ns

12

480 ns

12

INC Rn

08..0F

1

40 ns

12

480 ns

12

INC direct

05

2

80 ns

12

480 ns

6

INC @Ri

06..07

2

80 ns

12

480 ns

6

INC DPTR

A3

1

40 ns

24

960 ns

24

DEC A

14

1

40 ns

12

480 ns

12

DEC Rn

18..1F

1

40 ns

12

480 ns

12

Maxim Integrated