Timer/counter control (tcon), Timer/counter control (tcon) -16 – Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

Page 24

4-16

Ultra-High-Speed Flash

Microcontroller User’s Guide

STOP

Bit 1

IDLE

Bit 0

Stop Mode Select. Setting this bit stops program execution, halts the CPU oscillator and internal

timers, and places the CPU in a low-power mode. This bit always be reads as a 0. Setting this bit

causes the CTM bit (PMR.4) to be cleared. Setting both the STOP bit and the IDLE bit causes the

device to enter stop mode; however, doing this is not advised.

Idle Mode Select. Setting this bit stops program execution but leaves the CPU oscillator, timers,

serial ports, and interrupts active. This bit is always read as a 0. Setting both the STOP bit and the

IDLE bit causes the device to enter stop mode; however, doing this is not advised.

TF1

Bit 7

TR1

Bit 6

TF0

Bit 5

TR0

Bit 4

IE1

Bit 3

IT1

Bit 2

IE0

Bit 1

IT0

Bit 0

Timer 1 Overflow Flag. This bit indicates when Timer 1 overflows its maximum count as defined

by the current mode. This bit can be cleared by software and is automatically cleared when the

CPU vectors to the Timer 1 interrupt service routine.

0 = No Timer 1 overflow has been detected.

1 = Timer 1 has overflowed its maximum count.

Timer 1 Run Control. This bit enables/disables the operation of Timer 1.

0 = Timer 1 is halted.

1 = Timer 1 is enabled.

Timer 0 Overflow Flag. This bit indicates when Timer 0 overflows its maximum count as defined

by the current mode. This bit can be cleared by software and is automatically cleared when the

CPU vectors to the Timer 0 interrupt service routine or by software.

0 = No Timer 0 overflow has been detected.

1 = Timer 0 has overflowed its maximum count.

Timer 0 Run Control. This bit enables/disables the operation of Timer 0.

0 = Timer 0 is halted.

1 = Timer 0 is enabled.

Interrupt 1 Edge Detect. This bit is set when an edge/level of the type defined by IT1 is detected.

If IT1 = 1, this bit remains set until cleared in software or until the start of the External Interrupt 1

service routine. If IT1 = 0, this bit inversely reflects the state of the INT1 pin.

Interrupt 1 Type Select. This bit selects whether the INT1 pin detects edge- or level-triggered

interrupts.

0 = INT1 is level triggered.

1 = INT1 is edge triggered.

Interrupt 0 Edge Detect. This bit is set when an edge/level of the type defined by IT0 is detected.

If IT0 = 1, this bit remains set until cleared in software or until the start of the External Interrupt 0

service routine. If IT0 = 0, this bit inversely reflects the state of the INT0 pin.

Interrupt 0 Type Select. This bit selects whether the INT0 pin detects edge- or level-triggered

interrupts.

0 = INT0 is level triggered.

1 = INT0 is edge triggered.

R = Unrestricted read, W = Unrestricted write, -n = Value after reset

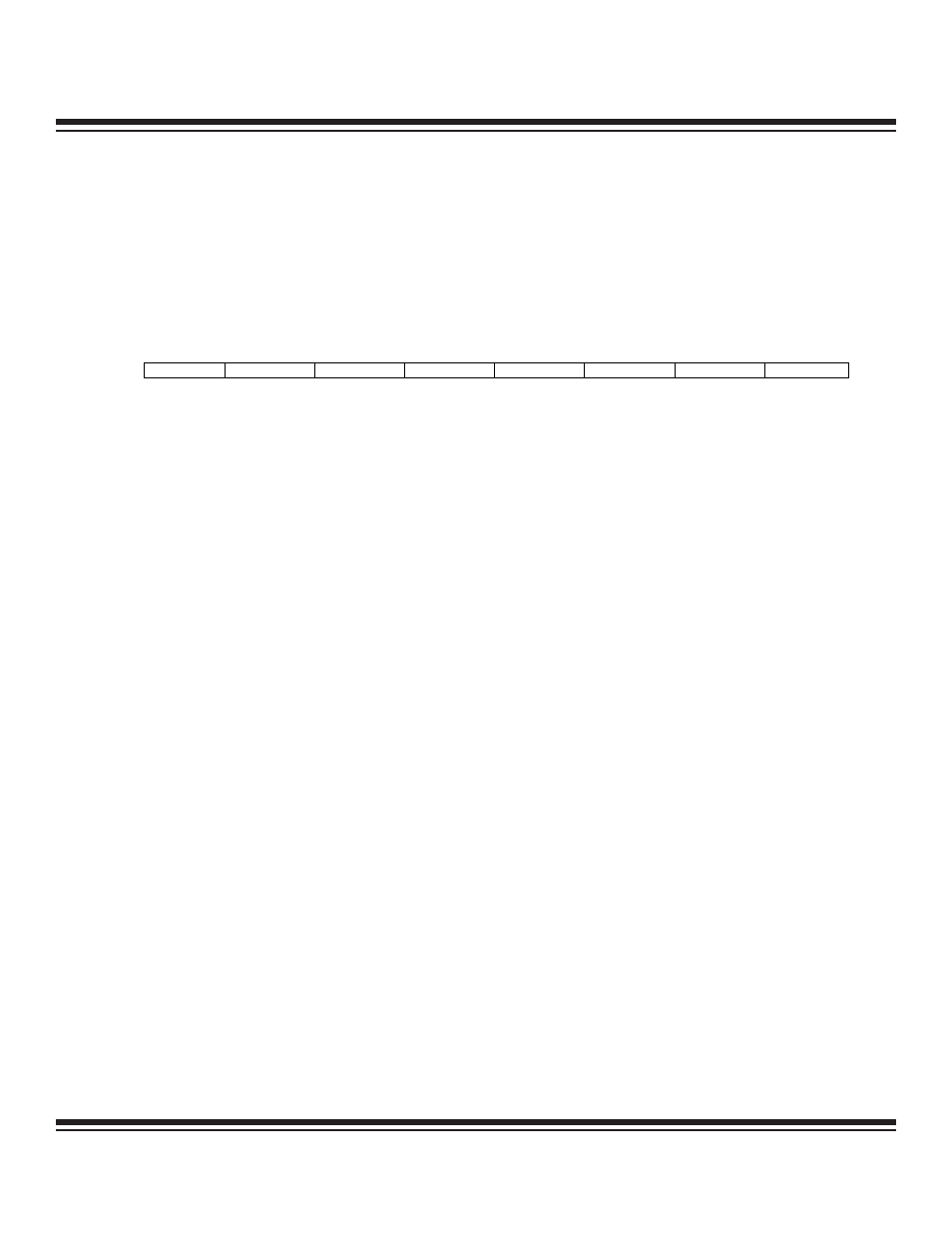

Timer/Counter Control (TCON)

7

6

5

4

3

2

1

0

SFR 88h

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

RW-0

Maxim Integrated