Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

Page 156

14-4

Ultra-High-Speed Flash

Microcontroller User’s Guide

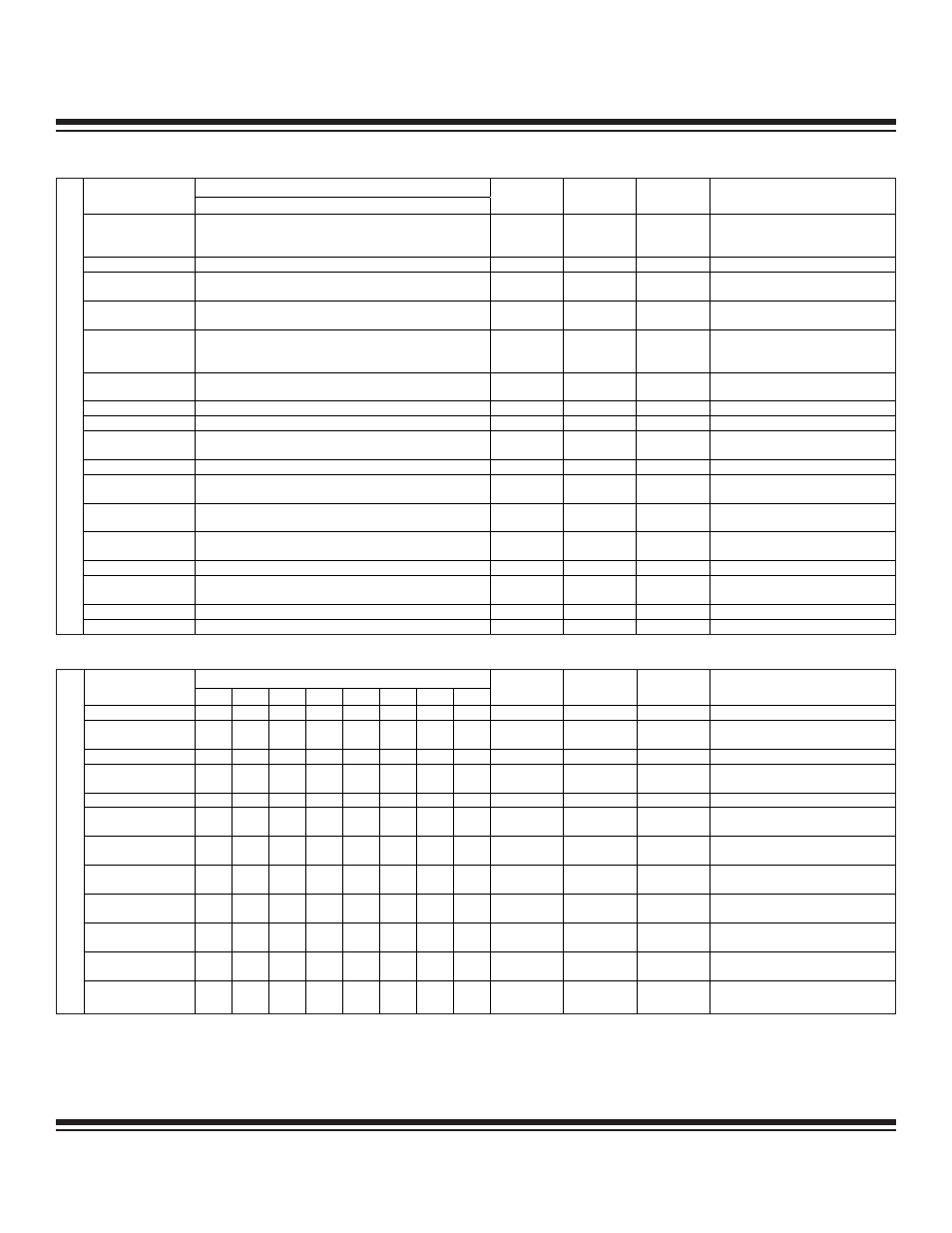

INSTRUCTION CODE

MNEMONIC

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

HEX

BYTE

CYCLE

EXPLANATION

MOV direct,

#data

0

a

7

d

7

1

a

6

d

6

1

a

5

d

5

1

a

4

d

4

0

a

3

d

3

1

a

2

d

2

0

a

1

d

1

1

a

0

d

0

75

Byte 2

Byte 3

3

3

(direct) = #data

MOV @Ri, A

1

1

1

1

0

1

1

i

F6-F7

1

1

((Ri)) = A

MOV @Ri,

direct

1

a

7

0

a

6

1

a

5

0

a

4

0

a

3

1

a

2

1

a

1

i

a

0

A6-A7

Byte 2

2

2

((Ri)) = (direct)

MOV @Ri,

#data

0

d

7

1

d

6

1

d

5

1

d

4

0

d

3

1

d

2

1

d

1

i

d

0

76-77

Byte 2

2

2

((Ri)) = #data

MOV DPTR,

#data16

1

d

7

d

7

0

d

6

d

6

0

d

5

d

5

1

d

4

d

4

0

d

3

d

3

0

d

2

d

2

0

d

1

d

1

0

d

0

d

0

90

Byte 2

Byte 3

3

3

(DPTR) = #data

15-0

(DPH) = #data

15-8

(DPL) = #data

7-0

MOVC A, @A +

DPTR

1

0

0

1

0

0

1

1

93

1

3

(A) = ((A) + (DPTR))

MOVC A, @A + PC

1

0

0

0

0

0

1

1

83

1

3

(A) = ((A) + (PC))

MOVX A, @Ri

1

1

1

0

0

0

1

i

E2-E3

1

2

(A) = ((Ri))

MOVX

@DPTR

1

1

1

0

0

0

0

0

E0

1

2

(A) = ((DPTR))

MOVX @Ri, A

1

1

1

1

0

0

1

i

F2-F3

1

2

((Ri)) = (A)

MOVX

@DPTR,A

1

1

1

1

0

0

0

0

F0

1

2

((DPTR)) = (A)

PUSH direct

1

a

7

1

a

6

0

a

5

0

a

4

0

a

3

0

a

2

0

a

1

0

a

0

C0

Byte 2

2

2

(SP) = (SP) + 1

((SP)) = (direct)

POP direct

1

a

7

1

a

6

0

a

5

1

a

4

0

a

3

0

a

2

0

a

1

0

a

0

D0

Byte 2

2

2*

(direct) = ((SP))

(SP) = (SP) - 1

XCH A, Rn

1

1

0

0

1

n

2

n

1

n

0

C8-CF

1

2

(A)

⇄ (Rn)

XCH A, direct

1

a

7

1

a

6

0

a

5

0

a

4

0

a

3

1

a

2

0

a

1

1

a

0

C5

Byte 2

2

3

(A)

⇄ (direct)

XCH A, @Ri

1

1

0

0

0

1

1

i

C6-C7

1

3

(A)

⇄ ((Ri))

D

A

T

A

T

R

A

N

S

F

E

R

XCHD A, @Ri

1

1

0

1

0

1

1

i

D6-D7

1

3

(A

3-0

)

⇄ ((Ri

3-0

))

INSTRUCTION CODE

MNEMONIC

D

7

D

6

D

5

D

4

D

3

D

2

D

1

D

0

HEX

BYTE

CYCLE

EXPLANATION

CLR C

1

1

0

0

0

0

1

1

C3

1

1

(C) = 0

CLR bit

1

b

7

1

b

6

0

b

5

0

b

4

0

b

3

0

b

2

1

b

1

0

b

0

C2

Byte 2

2

2*

(bit) = 0

SETB C

1

1

0

1

0

0

1

1

D3

1

1

(C) = 1

SETB bit

1

b

7

1

b

6

0

b

5

1

b

4

0

b

3

0

b

2

1

b

1

0

b

0

D2

Byte 2

2

2*

(bit) = 1

CPL C

1

0

1

1

0

0

1

1

B3

1

1

(C) = (C)

CPL bit

1

b

7

0

b

6

1

b

5

1

b

4

0

b

3

0

b

2

1

b

1

0

b

0

B2

Byte 2

2

2*

(bit) = (bit)

ANL C, bit

1

b

7

0

b

6

0

b

5

0

b

4

0

b

3

0

b

2

1

b

1

0

b

0

82

Byte 2

2

2

(C) = (C) AND (bit)

ANL C, bit

1

b

7

0

b

6

1

b

5

1

b

4

0

b

3

0

b

2

0

b

1

0

b

0

B0

Byte 2

2

2

(C) = (C) AND (bit)

ORL C, bit

0

b

7

1

b

6

1

b

5

1

b

4

0

b

3

0

b

2

1

b

1

0

b

0

72

Byte 2

2

2

(C) = (C) OR (bit)

ORL C, bit

1

b

7

0

b

6

1

b

5

0

b

4

0

b

3

0

b

2

0

b

1

0

b

0

A0

Byte 2

2

2

(C) = (C) OR (bit)

MOV C, bit

1

b

7

0

b

6

1

b

5

0

b

4

0

b

3

0

b

2

1

b

1

0

b

0

A2

Byte 2

2

2

(C) = (bit)

B

O

O

L

E

A

N

V

A

R

IA

B

L

E

M

A

N

IP

U

L

A

T

IO

N

MOV bit, C

1

b

7

0

b

6

0

b

5

1

b

4

0

b

3

0

b

2

1

b

1

0

b

0

92

Byte 2

2

2

(bit) = (C)

Maxim Integrated

Maxim Integrated