Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

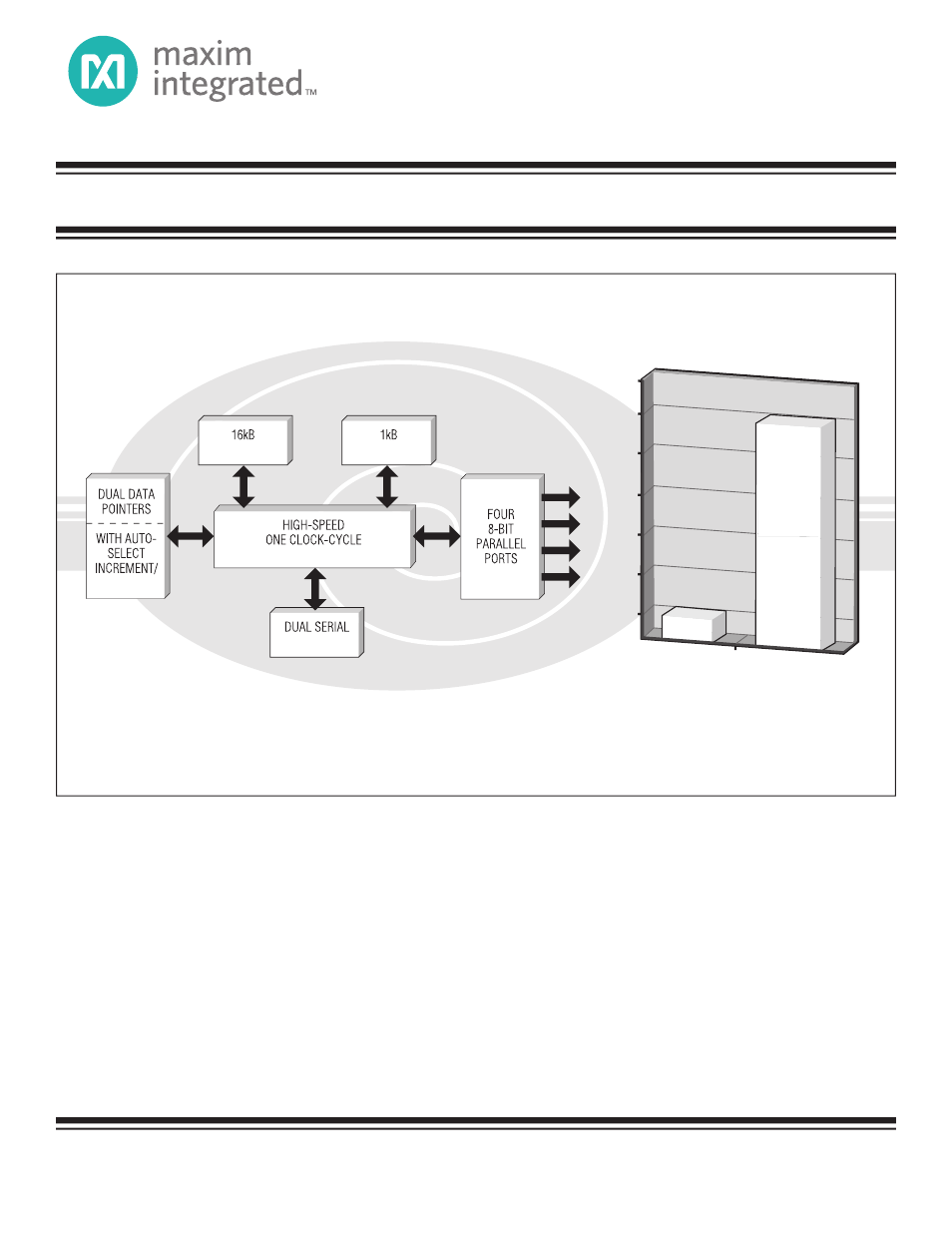

Functional diagrams

Functional Diagrams

Pin Configurations appear at end of data sheet.

Functional Diagrams continued at end of data sheet.

UCSP is a trademark of Maxim Integrated Products, Inc.

For pricing, delivery, and ordering information, please contact Maxim Direct

at 1-888-629-4642, or visit Maxim’s website at www.maximintegrated.com.

DECREMENT

PORTS

8051 MICROPROCESSOR

FLASH MEMORY

SRAM

1

5

25

0

33

ULTRA-HIGH-SPEED

FLASH

MICROCONTROLLER

ORIGINAL

8051

MIPS

ULTRA-HIGH-SPEED FLASH MICROCONTROLLER USER’S GUIDE

Rev: 11; 11/11

The Ultra-High-Speed Flash Microcontroller User’s Guide should be used in conjunction with the data sheet(s) for all ultra-high-speed flash microcontrollers.

Table of contents

Document Outline

- TABLE OF CONTENTS

- SECTION 1: INTRODUCTION

- SECTION 2: ORDERING INFORMATION

- SECTION 3: ARCHITECTURE

- SECTION 4: PROGRAMMING MODEL

- Memory Organization

- Memory Map

- Register Map

- Bit Addressable Locations

- Working Registers

- Stack

- Addressing Modes

- Program Status Flags

- Special-Function Register Lo...

- Special-Function Registers

- Port 0 (P0)

- Stack Pointer (SP)

- Data Pointer Low 0 (DPL)

- Data Pointer High 0 (DPH)

- Data Pointer Low 1 (DPL1)

- Data Pointer High 1 (DPH1)

- Data Pointer Select (DPS)

- Power Control (PCON)

- Timer/Counter Control (TCON)

- Timer Mode Control (TMOD)

- Timer 0 LSB (TL0)

- Timer 1 LSB (TL1)

- Timer 0 MSB (TH0)

- Timer 1 MSB (TH1)

- Clock Control (CKCON)

- Port 1 (P1)

- External Interrupt Flag (EXIF)

- Timer and Serial Port Clock ...

- Serial Port 0 Control (SCON0)

- Serial Data Buffer 0 (SBUF0)

- Revision ID (RID)

- Address Control (ACON)

- Port 2 (P2)

- Interrupt Enable (IE)

- Slave Address Register 0 (SA...

- Slave Address Register 1 (SA...

- Port 3 (P3)

- Interrupt Priority 1 (IP1)

- Interrupt Priority 0 (IP0)

- Slave Address Mask Enable Re...

- Slave Address Mask Enable Re...

- Serial Port 1 Control (SCON1)

- Serial Data Buffer 1 (SBUF1)

- ROM Size Select (ROMSIZE)

- Power Management Register (PMR)

- Status Register (STATUS)

- Timed Access Register (TA)

- Timer 2 Control (T2CON)

- Timer 2 Mode (T2MOD)

- Timer 2 Capture LSB (RCAP2L)

- Timer 2 Capture LSB (RCAP2H)

- Timer 2 LSB (TL2)

- Timer 2 MSB (TH2)

- Program Status Word (PSW)

- Watchdog Control (WDCON)

- Accumulator (A or ACC)

- Extended Interrupt Enable (EIE)

- B Register (B)

- Extended Interrupt Priority ...

- Extended Interrupt Priority ...

- SECTION 5: CPU TIMING

- SECTION 6: MEMORY ACCESS

- Internal Flash Memory

- ROMSize Feature

- Flash Security Block/Lock Bits

- Option Control Register Byte

- Internal SRAM Memory

- Program Memory Interface—Non...

- Program Memory Interface—Pag...

- Data Memory Interface

- Page Mode 1 Data Memory Timi...

- Page Mode 1 Data Memory Timi...

- Page Mode 1 Data Memory Timi...

- Page Mode 2 Data Memory Timi...

- Data Memory Access

- SECTION 7: POWER MANAGEMENT

- SECTION 8: RESET CONDITIONS

- SECTION 9: INTERRUPTS

- SECTION 10: I/O PORTS

- SECTION 11: PROGRAMMABLE TIMERS

- SECTION 12: SERIAL I/O

- SECTION 13: TIMED-ACCESS PROTECTION

- SECTION 14: INSTRUCTION SET DETAILS

- SECTION 15: PROGRAM LOADING

- REVISION HISTORY