Power management modes, Power management modes -9, Table 7-3. power management and status bit summary – Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

Page 101

7-9

Power Management Modes

Power consumption in CMOS microcontrollers is a function of operating frequency. The power management mode (PMM) feature allows

software to dynamically match operating frequency and current consumption with the need for processing power. Instead of the default

one clock per machine cycle, PMM utilizes 1024 clocks per cycle to conserve power.

Several special features have been added to enhance the function of the PMM. The switchback feature allows the device to almost

instantaneously return to divide-by-1 mode upon detection of an enabled external interrupt or the receipt of a falling edge on a serial

port receiver pin. The advantages of this become apparent when one calculates the increased interrupt service time of a device oper-

ating in PMM. In addition, a device operating in PMM would normally be unable to sample an incoming serial transmission to proper-

ly receive it. The switchback feature, explained below, allows a device to return to divide-by-4 operation in time to receive incoming

serial port data and process interrupts with no loss in performance.

A status register (STATUS;C5h) prevents the device from accidentally reducing the clock rate during the servicing of an external inter-

rupt or serial port activity. This register can be interrogated to determine whether an interrupt is in progress, or if serial port activity is

occurring. Based on this information the software can delay or reject a planned change in the clock divider rate.

In addition, the ultra-high-speed flash microcontroller has the capability to operate from the internal ring oscillator during normal oper-

ation, not only during the crystal warmup period. Table 7-3 summarizes the new control bits associated with the power management

features.

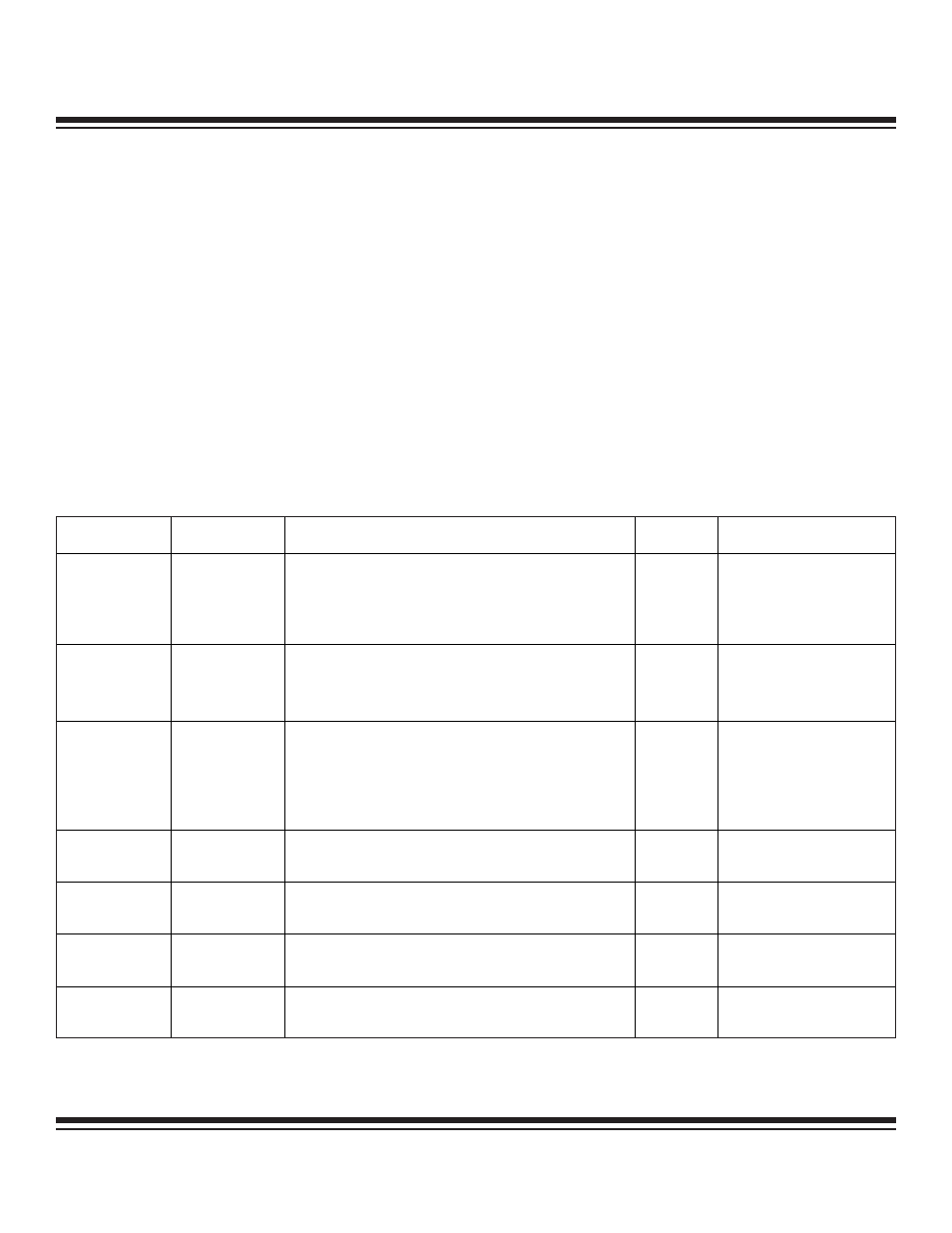

Table 7-3. Power Management and Status Bit Summary

BIT NAME

LOCATION

FUNCTION

RESET

STATE

READ/WRITE ACCESS

CD1, CD0

PMR.7–6

Clock divider control

CD1 CD0 osc cycles per system clock cycle

0

0

Crystal multiplier

0

1

Reserved

1

0

1 (reset default)

1

1

1024 (PMM)

10

Write: 10 anytime;

00, 01, and 11 only when

previously in 10 state.

Unrestricted read.

SWB

PMR.5

Switchback enable

0 = Interrupts and serial port activity will not affect clock divider

control bits

1 = Enabled interrupts and serial port activity will cause a

switchback

0

Unrestricted

PIS2:PIS0

STATUS.7:5

Priority Interrupt Status

101 = Level 4 interrupt (power fail) in progress

100 = Level 3 interrupt in progress

011 = Level 2 interrupt in progress

010 = Level 1 interrupt in progress

001 = Level 0 interrupt in progress

000 = No interrupt in progress

0

Read only

SPTA1

STATUS.3

Serial port 1 transmitter activity status

0 = Serial port 1 transmitter inactive

1 = Serial port 1 transmitter active

0

Read only

SPRA1

STATUS.2

Serial port 1 receiver activity status

0 = Serial port 1 receiver inactive

1 = Serial port 1 receiver active

0

Read only

SPTA0

STATUS.1

Serial port 0 transmitter activity status

0 = Serial port 0 transmitter inactive

1 = Serial port 0 transmitter active

0

Read only

SPRA0

STATUS.0

Serial port 0 receiver activity status

0 = Serial port 0 receiver inactive

1 = Serial port 0 receiver active

0

Read only

Ultra-High-Speed Flash

Microcontroller User’s Guide

Maxim Integrated